編輯:好睏 LRS

【新智元導讀】由聖母大學史弋宇教授和匹茲堡大學胡京通教授領銜的90後華人伉儷,姜煒文博士與楊蕾博士兩年前的研究如今修成正果,斬獲IEEE TCAD的最佳和DAC的University Demo雙項冠軍,可以說是理論和實踐兩開花!並且這篇論文也是開創了NAS的一個新領域,拉開了神經網路與硬體協同搜尋的新時代。

開發AI模型就像一個堆積木的過程,透過組合各種可以用到的網路層來找到一個性能更強的網路。

後來研究人員發現這個搜尋過程其實也可以自動化完成。

神經架構搜尋(Neural Architecture Search,NAS)的出現極大推進了AI向各行業進軍的速度,甚至在某些任務上已經能夠媲美人類專家了,並且還能發現一些人類之前未曾提出過的網路結構,可以說是極大提升了神經網路的使用和設計效率。

但神經網路的訓練、推理和部署從來都不只是軟體工程師的事,哪有什麼歲月靜好,只是各位硬體設計師一直在默默負重前行。

訓練好的神經網路模型有可能部署在各種各樣的硬體架構上,而硬體的架構反過來也會影響著模型的效能、吞吐量等等。

兩年前,就算考慮了硬體的NAS研究,也都只是在固定硬體架構的情況下琢磨如何提高效能,直到這篇論文的出現。

https://arxiv.org/pdf/1907.04650.pdf

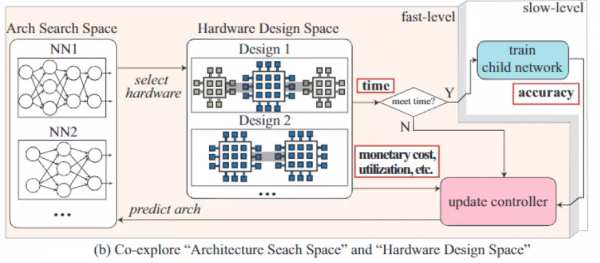

這篇論文提出了一個全新的NAS框架,同時考慮了神經架構搜尋空間(neural architecture search space)和硬體設計空間(hard design space)來找到和硬體匹配的最佳網路架構,這種方式能夠最大限度地提高模型的效能和執行效率。

在ImageNet上的實驗也證明了採用協同搜尋的NAS可以在精度不變的情況下,吞吐量提高35.24%,能量效率提高54.05%。

論文的成果經過兩年時間的檢驗後,最近獲得兩項大獎。一項是代表理論的TCAD最佳論文獎,另一項是代表應用研究的University Demo冠軍,擊敗了來自MIT, University of Virginia等10所高校。可以說是文體兩開花了。

論文由重慶大學博士伉儷姜煒文和楊蕾在聖母大學史弋宇教授和匹茲堡大學胡京通教授指導下完成。

第一作者姜煒文博士是喬治梅森大學助理教授,除了NAS領域,他還建立了第一個神經網路/量子計算協同設計框架QuantumFlow,證明了在量子計算機上設計神經網路的量子優勢,2021年也是一口氣在Nature子刊上發了三篇論文。

對於此次拿獎,姜煒文博士表示:「該獲獎工作是我們一些列軟硬協同神經網路加速工作的基礎,這些工作先後在DAC,CODES+ISSS,ASP-DAC會議上獲得多次提名最佳論文,這次終於修成正果。」

楊蕾博士是新墨西哥大學助理教授,目前主要從事系統級自動化機器學習應用的工作。

史弋宇博士於2021年在聖母大學晉升為終身正教授,其帶領團隊在過去1年發表了4篇Nature子刊。

胡京通博士於2020年在匹茲堡大學晉升終身副教授,並於2021年獲得William Kepler Whiteford Faculty Fellow。

史弋宇教授表示:「我們軟硬協同神經網路加速的工作除了TCAD的best paper以外,具體在實際產品上的應用還在DAC的University Demo拿了first place。希望這方面接下來還能有所突破。」

經典回顧

儘管NAS在各種任務,包括影象分類、影象分割和語言建模的模型架構設計中取得了巨大成功,但除了準確性之外,我們也應該考慮推理的時間效能(如延遲或吞吐量)。

隨著AI的發展,大量雲計算平臺和邊緣計算裝置都能夠採用能自由設計硬體的FPGA,相比傳統的專用專用積體電路ASIC,FPGA能夠極大提升電路的硬體設計空間,從而找到一個能讓神經網路發揮最佳效能的硬體電路。

所以如果有一個模型能夠同時設計神經網路架構和FPGA硬體架構,那效能豈不是更強?

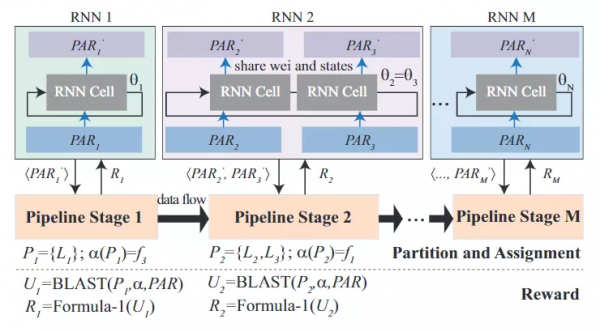

文中提出的HW/SW 協同搜尋的框架包含一個基於RNN的控制器和兩個層次的搜尋,其中子網路中的每個RNN的單元在面對不同的最佳化目標時都會被重組(reorganized)。

在第一層的快速搜尋中主要包含四步:

1、以機率p預測一個模型架構

2、在滿足吞吐量限制條件的情況下,搜尋設計空間來生成一個pipelined FPGA系統

3、根據流水線的結構,重組控制器中的RNN單元

4、使用強化學習最大化pipeline的效率來更新控制器引數

在重組和更新控制器時,由於我們的生成目標是找到更高硬體利用率的子網路,所以採用的策略是最大化平均硬體利用率。

最大化平均硬體利用率和最大化每個硬體的利用率之間就是全域性和區域性的區別,如果要找到全域性最優解,那所搜尋的設計空間要比區域性空間更大,基本是指數級的。

所以為了有效地搜尋設計空間,研究人員選擇了局部策略,最大化不同流水線階段的硬體利用率,並且根據確定的pipeline結構重組控制器中的RNN單元。

對於一個pipeline的多個層,RNN單元的權重和狀態都是共享的,所以N個pipeline只需要N個RNN單元就可以最大限度地提高每個FPGA pipeline階段的硬體利用率。

在第二層時,研究人員對對第一層得到的子網路進行訓練,訓練資料中保留一部分作為驗證集。在訓練完畢後將根據生成模型的準確率和pipeline效率作為評價標準生成一個獎勵來更新RNN控制器。如果第一層生成的子網路都不符合吞吐量的要求,將會產生一個負獎勵。

在第二層預測後,控制器將會在架構搜尋空間中預測一個新的子網路,用於下一次的快速搜尋。

在第一層更新控制器中的RNN單元之前,需要對所有RNN單元權重進行快照儲存。根據確定的pipeline結構,RNN單元再被重組,以便為之前獲得的硬體設計(即pipeline結構)生成更好的子網路。

在進入慢速搜尋層後,控制器中的RNN單元將使用先前儲存的權重快照進行恢復。然後以準確度為目標來訓練子網路,然後利用獎勵函式更新恢復RNN。透過這種迭代方式,準確率將會不斷提升,並且找到一個最佳的硬體設計。

和以往的研究不同的是,文中提出的RNN控制器集成了多個RNN單元,能夠同時對兩個層進行最佳化,在效率和準確率之間更好地權衡和最佳化。

總的來說,在第一層中,RNN只對給定的模型架構進行最佳化;而在第二層的時候RNN將會確定模型的骨架網路和pipeline結構。

結果分析

由於硬體容量的限制,所有架構的引數都少於100萬個,這不可避免地導致了準確性的損失。

但是依然可以看到,OptSW搜尋的架構在CIFAR-10上仍可以達到85.19%的測試準確率,並在ImageNet上達到70.24%的top-1準確率。這些結果證明了協同搜尋方法在資源有限的情況下的有效性。

此外,OptSW優於硬體感知NAS,在CIFAR-10和ImageNet上分別取得了54.37%和35.24%的吞吐量,以及56.02%和54.05%的能效。

與順序最佳化相比,OptSW在CIFAR-10上的吞吐量和能效分別提高了16.34%和28.79%;在ImageNet上,它也能略微提高吞吐量,並實現37.84%的能效提高。

在CIFAR-10和ImageNet上的準確性、pipeline效率、吞吐量和能效的對比

透過在快速搜尋層面進行有效的早期階段修剪,協同搜尋可以極大地加快搜索的過程,並在CIFAR-10和ImageNet上分別實現了159倍和136倍的速度。

與傳統的控制器中只有一個RNN的硬體感知NAS相比,具有多個RNN的協同搜尋框架可以將設計空間從O(∏i Di)大幅縮小到O(∑i Di),其中Di是第i個管道階段的設計空間大小。

從表中「訓練架構」中可以看到,協同搜尋與硬體感知NAS相比,訓練的架構要少得多。由於需要訓練的架構數量與設計空間的大小成正比,因此協同搜尋也實現了顯著的速度提升。

硬體感知NAS和協同搜尋的歸一化搜尋時間的對比

參考資料:

https://ieee-ceda.org/awards/ieee-transactions-computer-aided-design-donald-o-pederson-best-paper-award

https://www.sigda.org/sigda-events/ubooth/