“人們聲稱摩爾定律已經結束,但在我看來,情況並非如此。摩爾定律可以透過在第三維度上的發展而繼續下去。”

在半導體行業中,為了使摩爾定律能夠多“續命”幾年,各家廠商都在努力縮小電晶體的尺寸,直到最小的部分只有一個原子的厚度。不幸的是,這對矽來說是行不通的,它的半導體特性要求其必須以三維的形態呈現。

但是有一類材料,即使它們是二維的,也能作為半導體發揮作用。一些最大的晶片公司和研究機構的最新結果顯示,一旦矽達到極限,這些二維半導體可能是一條很好的發展道路。

在本週於舊金山舉行的IEEE國際電子器件會議(IEDM)上,英特爾、斯坦福大學(Stanford University)和臺積電(TSMC)的研究人員針對製造二維電晶體最棘手的障礙之一——在半導體與金屬接觸的地方出現了電阻峰值——提出了單獨的解決方案。

同時,比利時微電子研究中心(IMEC)的工程師們展示了他們如何為商業級的製造工藝掃清道路,並展示了未來的二維電晶體可能有多小。北京和武漢的研究人員已經制造出了最先進的矽器件型別的二維等效物。

“人們聲稱摩爾定律已經結束,但在我看來,情況並非如此。摩爾定律可以透過在第三維度上的發展而繼續下去。”斯坦福大學電氣工程系教授Krishna Saraswat說,“為此,你需要二維半導體或類似的技術。”

目前,Saraswat正與斯坦福大學的教授Eric Pop和H.-S. Philip Wong合作研究三維晶片。由於二維半導體具有縮小尺寸和相對較低的加工溫度的潛力,因此它們可以分多層建造。

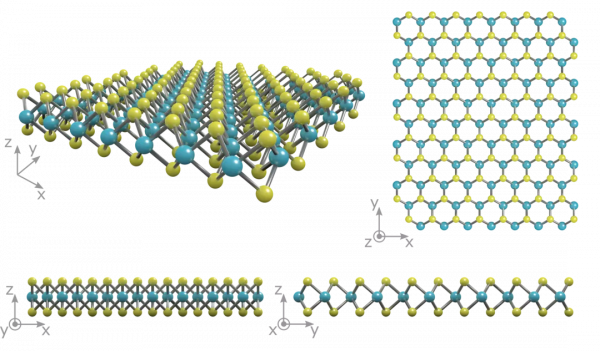

二維半導體屬於一類叫做過渡金屬二氯化物的材料。在這些材料中,研究得最好的是二硫化鉬。理論上,電子應該比二硫化鉬更快地穿過二硫化鎢這種二維材料。但在英特爾公司的實驗中,二硫化鉬器件更勝一籌。

現實中,二維半導體面臨的最大障礙是與它們建立低電阻連線。這個問題被稱為“費米能級的釘扎”(Fermi-level pinning),它的意思是,金屬觸點和半導體的電子能量不匹配,對電流的流動產生了一個高電阻障礙。

這種肖特基勢壘的產生是因為介面附近的電子流向能量較低的材料,留下一個抵制電流的電荷耗盡區。現在的目標是使該區域變得儘可能微小,最好是電子可以輕而易舉地穿過它。

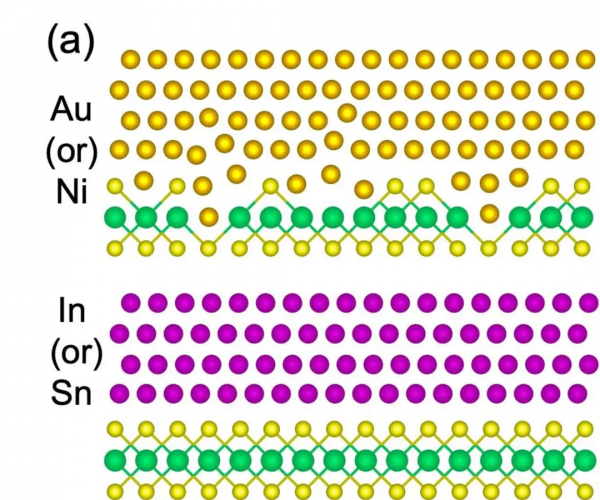

Saraswat的學生Aravindh Kumar提出了一個解決這個問題的方法,並在IEDM上進行了報告。在之前的研究中,黃金一直是用二硫化鉬形成電晶體的首選觸點。但是沉積金和其他高熔點金屬會破壞二硫化鉬,使屏障問題變得更糟。因此,Kumar用銦和錫進行了實驗,它們的熔點在數百攝氏度以下。

但這些數值太低了,以至於這些金屬在晶片加工和包裝過程的後半部分會融化,而這一過程將晶片暴露在高達300-500攝氏度的溫度下,更糟糕的是,這些金屬在加工過程中會被氧化。

在試圖解決後一個問題的同時,Kumar解決了前一個問題。答案是將低熔點金屬與金合金化。銦或錫首先沉積在二硫化鉬上,保護半導體,然後用金蓋住它們,以防止氧氣進入。

這個過程導致了錫-金合金具有270歐姆-微米的電阻,而銦-金具有190歐姆-微米。而且這兩種合金應該至少在450攝氏度下保持穩定。

但晶片製造商臺積電和英特爾分別找到了不同的解決方案——銻。臺積電企業研究部的低維研究經理Han Wang解釋說,其想法是透過使用半金屬作為接觸材料來減少半導體和接觸之間的能量障礙。

半金屬(如銻)是一種處於金屬和半導體之間的材料,具有零帶隙。由此產生的肖特基勢壘非常低,使得臺積電和英特爾裝置的電阻不必過高。

臺積電以前曾用另一種半金屬鉍來工作。但它的熔點太低。銻具有更好的熱穩定性,這意味著它將與現有的晶片製造工藝更加相容,使裝置的壽命更長,並使晶片製造工藝的後半部分具有更大的靈活性。

除了製造更好的裝置,IMEC的研究人員還對尋找在商用300毫米矽片上整合二維半導體的途徑十分感興趣。利用300毫米矽片,IMEC探索二維裝置最終可能達到多小。

研究人員使用二硫化鎢作為半導體,形成了雙柵電晶體,其中二硫化鎢被夾在控制流過的電流的頂部和底部電極之間。透過採用圖案技巧,他們成功地將頂部柵極縮小到5奈米以下。這個特定的裝置並沒有表現得特別好,但研究指出了改進它的方法。

另外,在本週晚些時候公佈的研究中,IMEC將展示300毫米相容的工藝最佳化步驟,透過包括鋁酸釓夾層等來改善二硫化鉬電晶體的特性。

儘管像IMEC這樣的雙柵器件是二維研究的標準,但北京大學和華中科技大學國家脈衝強磁場科學中心的工程師們將事情向前推進了一步。

如今的矽邏輯電晶體被稱為FinFET,其結構是電流透過一個垂直的矽片,並由一個垂在矽片三面的柵極控制。但是,為了繼續縮小器件的尺寸,同時仍然驅動足夠的電流透過它們,領先的晶片製造商正在轉向奈米片器件。在這些器件中,半導體帶被堆積起來;每條帶子的四面都被柵極包圍。

由吳燕慶領導的北京研究人員使用兩層二硫化鉬模擬了這種結構。結果發現,該裝置比其各部分的總和還要大。與他們的單層器件相比,二維奈米片的跨導率超過兩倍,這意味著在給定電壓下,它驅動的電流超過兩倍。

英特爾公司模擬了一個更加極端的堆疊式二維器件的版本。它的研究人員使用了六層二硫化鉬和只有5奈米的柵極長度,而不是北京裝置的兩層和100奈米。

與垂直高度相同、柵極長度為15奈米的模擬矽器件相比,該二維器件多裝了兩層奈米片,效能更好。儘管電子透過二硫化鉬的速度比透過矽的速度要慢,而且接觸電阻要高得多。

然後,吳燕慶和他的同事們朝著模仿矽裝置製造商的近期計劃邁出了另一步。根據定義,CMOS晶片是由一對N-MOS和P-MOS器件組成的。為了在相同面積的矽片上塞進更多的器件,晶片製造商希望將這兩種型別的器件堆疊在一起,而不是將它們並排放置。

英特爾在去年的IEDM上展示了這樣一種矽器件,稱為互補FET(CFET)。吳燕慶的團隊透過用二硒化鎢取代他們的堆疊裝置中的二硫化鉬層進行了同樣的嘗試。然後,透過修改源極和漏極之間的連線,二維CFET變成了一個倒相電路,其佔用空間基本上與一個單電晶體相同。

顯然,在二維半導體獲得批次生產之前,還有很多工作要做,但隨著接觸電阻方面取得的進展和新實驗所顯示的潛力,研究人員充滿希望。

參考資料:

https://spectrum.ieee.org/2d-semiconductors-and-moores-law