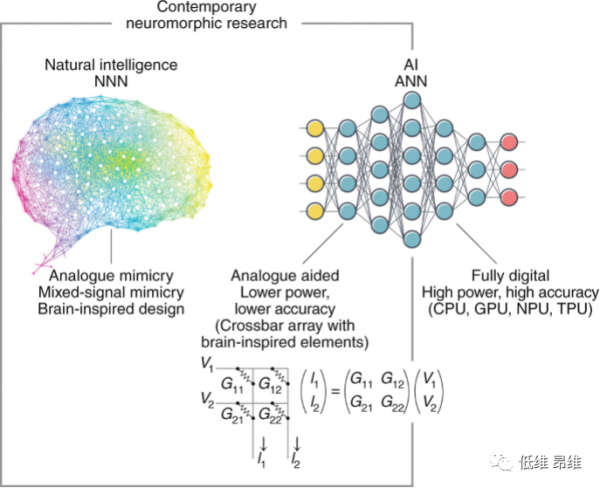

近年來,人類社會資料量的指數增長對高效、快速的以資料為中心的計算提出了越來越高的要求。傳統馮·諾依曼體系結構的數字硬體基於互補金氧半導體(CMOS)系統,由於其在資訊處理和儲存單元之間不斷傳輸資料,因此極大地限制了操作速度和能源效率。神經形態計算體系結構建立在密集非易失性儲存器縱橫制陣列上,旨在在儲存資料的確切位置進行原位計算,以解決瓶頸問題。然而,如何將這些陣列整合到晶片中仍然是學界和業界尚未克服的挑戰。

鑑於此,近期,由來自中國華中科大、中科院浙江大學、武漢大學和香港大學的研究人員在國際頂尖期刊Science上以2D materials-based homogeneous transistor-memory architecture for neuromorphic hardware為題發表文章,報道了一種全新的計算架構體系,透過在多疇鐵電LiNbO3單晶上鋪設二維WSe2薄膜來解決計算電晶體與儲存記憶體整合的問題,以構建具有模擬訊號處理和儲存器操作的可重構雙功能的“均勻整合”瞬態儲存器結構。透過這種方法,他們展示了具有增強和抑制特性的非易失性儲存器,並展示了幾個電晶體可用於在雙電晶體-雙電阻器配置中製造運算放大器和三值內容定址儲存器。這一全新架構為神經形態計算的發展開闢了全新的技術路徑,有望大大推動下一代類腦神經晶片的商業落地與應用。

圖1. 類腦計算示意圖。

圖源: Nature Electronics 4, 635–644 (2021)

在傳統的神經形態硬體中,基於異構裝置的外圍電路和儲存器通常是物理分離的。因此,探索這些元件的同質器件是改善模組整合和電阻匹配的關鍵。受二維材料鐵電接近效應的啟發,我們提出了一種鎢二硒化物-鈮酸鋰級聯結構,作為一種基本器件,起到非線性電晶體的作用,幫助設計模擬訊號處理運算放大器。該裝置還可作為非易失性儲存單元,實現儲存器操作功能。在此同構體系結構的基礎上,我們還研究了模擬訊號處理-儲存器操作整合系統的二元分類和三元內容定址儲存器的設計,以便在神經形態硬體中潛在地使用。

最近提出的基於各種新興奈米材料的以神經元為靈感的硬體有效地改進了神經網路,特別是二維材料。二維材料可以提供一個平臺來開發用於儲存器操作的電晶體架構,包括場效應電晶體、隧道電晶體、結電晶體、鐵電電晶體和鐵磁電晶體,因為它們具有豐富的靜電控制能力。基於二維材料的鐵電 場效應電晶體、鐵電雙極結電晶體和鐵電隧道電晶體由於鐵電材料與二維材料的強近端耦合,在可逆極化下表現出較大的通斷電阻比、快速操作、低功耗、非易失性電子控制和重量更新。因此,這些基於二維材料的鐵電近端耦合器件正在被深入研究用於神經形態計算,其中它們透過動態調製鐵電極化來程式設計上相鄰二維通道的導電性被用作儲存器。實現計算任務需要這些儲存器與外圍電路整合,因為模擬訊號處理在儲存器操作前後都是必不可少的。然而,外圍電路通常基於互補金氧半導體(CMOS)電晶體,因此儲存單元和外圍電路之間的異構結構導致它們的物理分離,使得有必要考慮晶片設計的模組整合相容性問題。此外,隨著裝置尺寸的縮小,如何在異構裝置架構之間實現有效的電阻匹配成為一個新的挑戰,這可能會阻礙對更高效能和能效的追求。因此,探索模擬訊號處理與儲存器操作的整合至關重要。

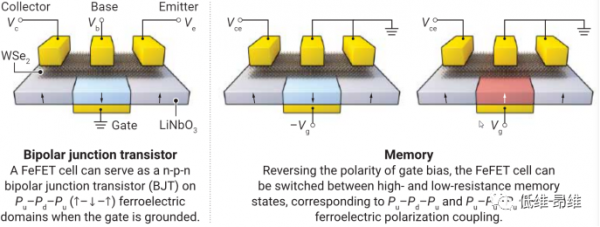

圖2. 鐵電場效應電晶體陣列作為二維導電薄膜,LiNb場效應電晶體是由LiNbO3晶體和LiNbO2晶體構成的。施加不同的電壓或接地會改變每個電池的功能,多個電池可以組合成更大的功能陣列。

圖源:Science 373, 1310-1311 (2021).

此外,利用模擬訊號處理-鐵電積體電路,還可以實現上述二維-鐵電積體電路的設計,從而緩解外圍電路的耦合問題。一方面,二維材料中的鐵極化鄰近感應非易失性電子選通使非線性電晶體的設計成為可能,包括p-n二極體和雙極結電晶體。另一方面,鐵極化可以調製雙極結電晶體中的內建電勢,從而實現具有改進的開關電阻比的非易失性儲存器功能。此外,可重構鐵極化疇可以無縫操縱二維材料中的陣列摻雜疇,顯示出製造具有增強緊湊性的大規模級聯器件的潛力。因此,提出了一種基於非易失性單元的整合化儲存器操作-模擬訊號處理體系結構,以及一種基於非易失性單元的整合化儲存器操作-模擬訊號處理體系結構。

在這項工作中,無縫排列的週期性極化LiNbO3疇形成了類似光柵的結構,有效地將WSe2通道裁剪成無縫排列的結。研究了模擬訊號處理、儲存器操作及其相應的級聯,以證明基於相同裝置架構的整合系統的成功,該整合系統包括一個跨越三個鐵電域的WSe2通道。我們的運算放大器是為模擬訊號處理設計的,帶有編碼突觸權重的記憶細胞與運算放大器級聯,以證明其在二進位制分類中的適用性。此外,具有雙管雙電阻配置的三元內容定址儲存器(TCAM)採用同質電晶體儲存器結構設計,高阻狀態(HRS)和低阻狀態(LRS)之間的比率為898.4。這種整合的系統架構為解決異構問題和改進神經形態應用提供了一種可行的方法。

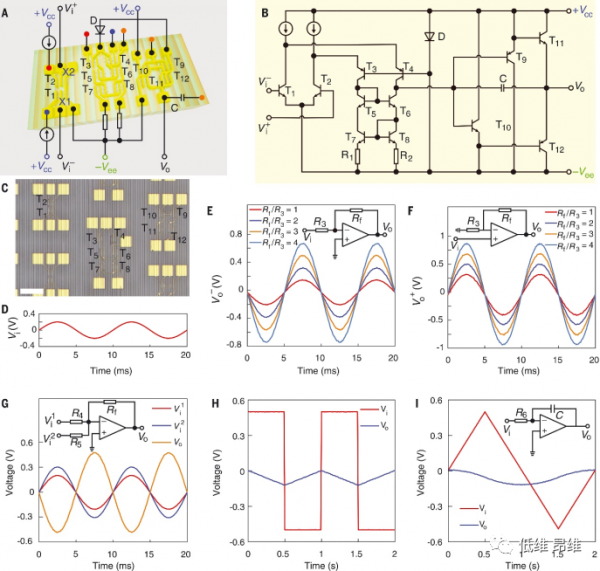

圖3. 基本裝置和效能機制。

圖源:Science 373, 1353-1358 (2021).

神經形態計算策略類似於人腦的工作模式,在這種模式下,資訊在一個由神經元和突觸組成的大規模連線網路中進行處理。然而,人腦在計算並行性和功耗方面遠遠優於所有神經形態硬體。這部分是因為神經形態硬體需要交叉選擇裝置和外圍電路的異構整合,以支援對NVM陣列的大規模並行訪問。隨著器件尺寸的縮小,在物理分離的異構元件中,模組整合不相容性和互連電阻失配變得更加突出。

鐵電體具有非易失性極化狀態,可透過施加外部電場以相反方向定向。傳統鐵電隨機存取儲存器採用金屬/鐵電/金屬三明治結構作為電容器與電晶體整合以形成單電晶體單電容單元。相比之下,鐵電場效應電晶體使用鐵電作為柵極來累積或耗盡導電溝道中的電荷載流子,從而導致可用於訊號處理和資訊儲存的溝道電阻中的非易失性變化。鐵電場效應電晶體顯示出非破壞性的讀取特性,不存在嚴重的縮放問題。最近,密集的研究集中在使用石墨烯以外的新興二維溝道材料(如強關聯氧化物、過渡金屬二鹵化物(TMD)和範德華異質結構)來更新鐵電場效應電晶體器件。這種新的組合是由一種潛在的有希望的替代傳統邏輯和記憶體技術所驅動的。

Tong等人選擇了幾層TMD WSe2作為鐵電場效應電晶體器件的半導體溝道,其中商業化的LiNbO3單晶作為底層鐵電絕緣體。對於單疇LiNbO3,鐵電場效應電晶體器件對於合格的記憶功能表現出典型的鐵電滯回曲線,其高電阻與低電阻之比約為200。在使用三疇LiNbO3絕緣體的情況下執行不同的儲存器工作模式,其中對於集電極和發射極端子下方的雙邊疇,鐵電極化狀態固定為向上(Pu),然而,中心疇的極化方向可以根據柵極電壓極性改變,即負偏壓下的向下極化(Pd)−正Vg(零柵極電壓)下的Vg和Pu。對齊三個Pu導致鐵電場效應電晶體儲存裝置的低電阻狀態,而Pu-Pd-Pu耦合導致高電阻狀態。從高到低的資料解析度明顯增加到∼106,為眾多突觸重量的調整提供了廣闊的空間。當柵極接地時,Tong等人還成功地將相同的三疇鐵電場效應電晶體器件裁剪成Pu-Pd-Pu疇上的n-p-n雙極結電晶體(雙極結電晶體)。

圖4. 模擬訊號處理的OPAMP。

圖源:Science 373, 1353-1358 (2021).

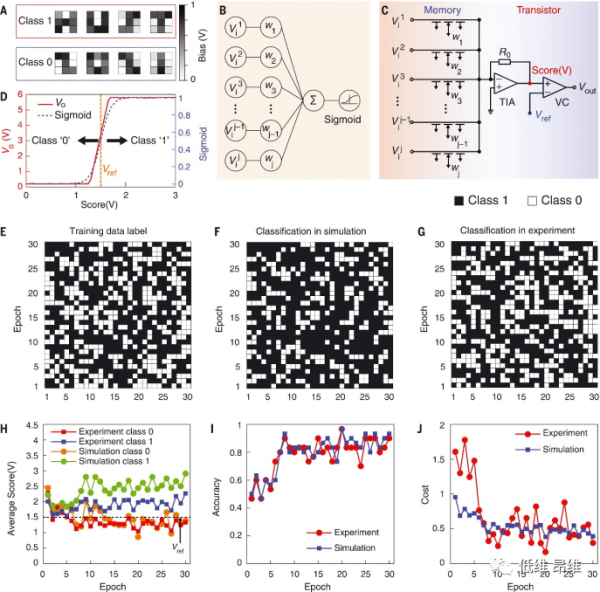

與許多儲存技術中的異構整合方案不同,Tong等人的體系結構在結構和功能上更為同質,因為一個額外的邏輯功能完美地編織在一個儲存單元中,單個鐵電場效應電晶體器件中的共生雙功能可以很容易地在不同的激勵模式下重新配置。將多個鐵電場效應電晶體級聯在一個密集陣列中,可以提供豐富的模組功能。它本質上減少了異構情況下面臨的整合困難,避免了模組整合不相容和電阻不匹配的問題。在新的體系結構中,可以消除記憶體和計算元素之間的遠距離資料移動,從而提供一個實現高頻寬和低延遲計算的平臺,這將大大降低神經形態晶片的製造門檻。Tong等人使用小陣列演示了神經形態計算的三個基本功能。作者在雙極結電晶體連線電路上實現了模擬訊號處理的運算放大器功能,與基於複雜C儲存器操作的系統相比功耗降低了一個數量級。基於鐵電場效應電晶體的低能比較器用於啟用功能,與電路中的跨阻放大器串聯。它們被整合在一個包含九個鐵電場效應電晶體儲存單元的陣列的後端,執行二進位制分類任務。經過訓練,作者透過模擬和實驗實現了模式標籤和預測類的識別。具有雙電晶體雙電容單元結構的三元內容定址儲存器允許並行搜尋海量資料集。這些同質結構在面積和能量效率方面優於CMOS操作結構。

進一步的,本文提出的同質計算結構有可能用於開發模擬-數字轉換器、數字-模擬轉換器和模擬濾波器,以構建更強大的神經形態系統。在這方面,高密度晶片是一個先決條件,儘管它對按順序堆疊分層鐵電場效應電晶體陣列的三維整合過程提出了巨大挑戰。鈮酸鋰晶體的低溫合成和高質量二維溝道材料的晶圓級沉積似乎是不可克服的障礙。需要努力實現其他與儲存器操作相容的二維鐵電體,如二氧化或碲化錫,以及光敏或熱敏通道材料,如相變超材料或異質結構,以形成大規模生產感官計算儲存整合晶片的更可行路線,促進目標識別、決策、自動駕駛和其他技術的人工智慧應用。

圖5. 模擬訊號處理-儲存器操作整合用於二進位制分類。

圖源:Science 373, 1353-1358 (2021).

總結與展望

二維材料是開發為神經形態電路設計的電晶體的一個有價值的平臺,因為它們的通道易於靜電控制,例如,當耦合到鐵電材料以製造鐵電場效應電晶體(鐵電場效應電晶體)時。然而,也需要外圍電路——比如感測器輸入的模擬到數字處理——這通常透過傳統的互補金氧半導體(CMOS)電晶體實現。因此,將此類系統整合到單個晶片上可能是一項挑戰。胡偉達、葉磊及其同事現在已經開發出一種同質電晶體設計,可用於儲存器和模擬訊號處理。

除了二進位制分類和三元內容定址儲存器設計外,本文提出的這種計算架構還適用於各種應用,包括數字計算和具有光學感測能力的人工神經系統。此外,這種計算架構還適用於模擬-數字轉換器、數字-模擬轉換器和模擬濾波器的設計。透過減小極化疇尺寸可以減小器件尺寸,從而提高電流增益和積分密度。較低的矯頑電壓有助於實現較低的功耗,這可以透過減小鈮酸鋰厚度或使用其他鐵材料來實現。

總而言之,受傳統CMOS晶片的啟發,本文提出了一種基於二維整合的神經形態模擬訊號處理-儲存器操作三維堆疊系統。這種同質電晶體儲存器結構將有助於在晶片上實現的神經形態計算,大大推動下一代類腦神經晶片的商業落地與應用。

參考文獻:

Lei Tong, Zhuiri Peng, Runfeng Lin, Zheng Li, Yilun Wang, Xinyu Huang, Kan-Hao Xue, Hangyu Xu, Feng Liu, Hui Xia, Peng Wang, Mingsheng Xu, Wei Xiong, Weida Hu, Jianbin Xu, Xinliang Zhang, Lei Ye, Xiangshui Miao, “2D materials-based homogeneous transistor-memory architecture for neuromorphic hardware”, Science 373, 1353-1358 (2021).