圖文摘要

單晶金剛石憑藉優異的力、熱、光、電等性質,在探測器、功率器件、量子計算等領域具有廣泛的應用前景,但大尺寸低缺陷高純度晶體的合成是制約其應用的主要瓶頸。作為兩種最常用的CVD手段,異質外延工藝相比同質外延工藝,由於不受籽晶尺寸的限制,在大尺寸單晶金剛石製備方面具有更顯著的技術優勢。

異質外延單晶金剛石合成工藝涉及異質襯底選擇、金剛石高密度形核、金剛石外延生長等過程,而Ir複合襯底和偏壓增強形核工藝是目前最優的異質襯底和形核手段。然而,由於受到Ir襯底-金剛石介面晶格失配的影響,所合成的金剛石往往表現出較高的位錯密度,這對其在電子器件領域的應用十分不利。因此,如何降低異質外延單晶金剛石中的位錯密度是該領域近年來研究的重要課題。

近日,哈爾濱工業大學朱嘉琦教授團隊在開展單晶金剛石異質外延生長研究工作的基礎上,對該領域的研究進展進行了詳細總結,在《新型炭材料》(New Carbon Materials)上發表最新綜述“Recent progress on controlling dislocation density and behavior during heteroepitaxial single crystal diamond growth”。

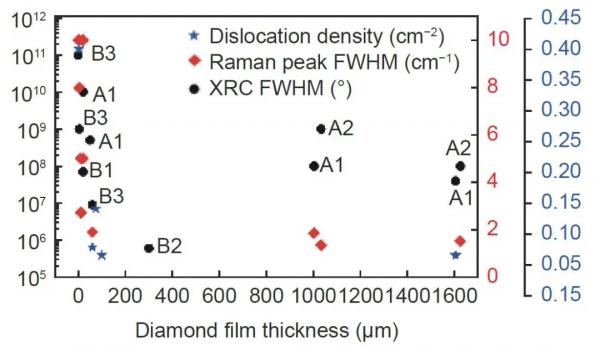

該文以降低Ir 襯底上異質外延金剛石膜中位錯密度為目標,首先對該過程中的位錯產生、型別、表徵等進行闡釋,然後從理論與工藝相結合的角度總結了加劇位錯反應(增加外延層厚度,偏軸襯底生長)、除去已有位錯(橫向外延過度生長,懸掛-橫向外延生長,圖形化形核生長)及其他方法(三維生長法、金屬輔助終止法、採用金字塔型襯底法)在降低金剛石位錯密度方面的最新進展,隨後結合大失配異質外延半導體體系降低位錯密度的經典理論,提出了襯底圖形化技術、超晶格緩衝層技術和柔性襯底技術等可透過抑制引入位錯來進一步降低位錯密度的研究方向,最後對本領域的發展現狀和未來展望進行了總結。如圖1所示為該文總結的降低異質外延金剛石內部位錯密度的具體手段。如圖2所示為目前所採用上述手段獲得的金剛石內部位錯密度比較,可以發現金剛石膜內位錯密度任然處於較高水平,尚需開發新一代位錯密度降低技術。

圖1 降低異質外延金剛石內部位錯密度的工藝及原理

圖2 不同手段獲得的金剛石內部位錯密度比較

哈爾濱工業大學博士研究生王偉華為第一作者,朱嘉琦教授為共同通訊作者。上述研究得到了國家重點研發計劃、廣東省重點研發計劃、國家傑出青年基金和國家自然科學基金的支援。

本文來源:新型炭材料