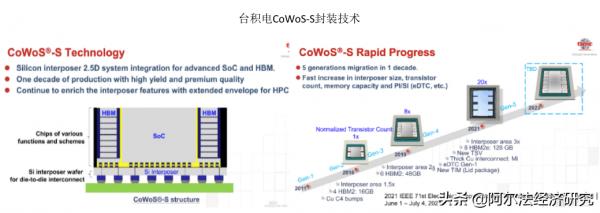

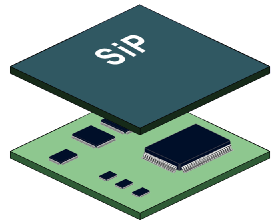

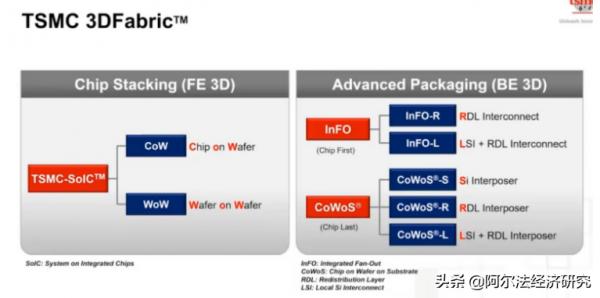

臺積電的3D Fabric先進封裝平臺由Chip Stacking和Advanced Packaging兩部分組成,前者就是所謂的前道晶片堆疊技術,由CoW和WoW組成SoIC技術平臺,也就是系統整合晶片技術,將多個小晶片Chiplet整合在一個面積更小與輪廓更薄的系統單晶片,就像一整個矽片一樣,典型特徵是沒有用到後端封裝中用到的凸點技術。後者是傳統意義上的後道封裝技術,由InFO和CoWoS兩大核心技術組成:

資料來源:臺積電3D Fabric技術平臺,公司官網整理,阿爾法經濟研究

臺積電力推的SoIC 2035年或實現微米內互連

臺積電在2018年4月的第24屆年度技術研討會上首次對外公佈了SoIC多晶片堆疊技術。SoIC技術提供CoW和WoW兩種鍵合方式,前者是將晶片透過Chip on Wafer的方式連線至矽片,可形成超高密度垂直堆疊,具有高效能、低功耗和最小RLC等特點;後者是透過晶圓堆疊工藝實現異構和同質3D矽整合,緊密的鍵合間距和薄TSV可實現最小寄生效應,從而獲得更好的效能、更低功耗、更小延遲和更小尺寸,適用於高良率節點和相同晶片尺寸的應用或設計,甚至支援3D整合:

資料來源:臺積電CoW和WoW技術,公司官網整理,阿爾法經濟研究

臺積電的SoIC整合的晶片在系統性能上優於原始的SoC,還可提供整合其他功能的靈活性。臺積電指出,SoIC將可滿足雲、網路和邊緣應用中不斷增長的計算、頻寬和延遲要求,CoW和WoW也為混合和匹配不同晶片功能、尺寸和技術節點提供出色的設計靈活性:

資料來源:臺積電SoIC技術性能優勢,公開資料整理,阿爾法經濟研究

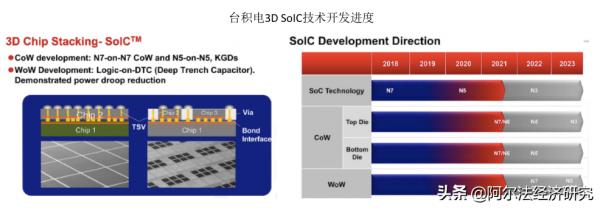

基於SoIC的3D晶片堆疊技術是臺積電先進封裝技術重點之一,公司在CoW方面正在開發N7-on-N7和N5-on-N5等技術,TSV的間距也將從9微米縮減到4.5微米。WoW方面開發的技術是Logic-on-Deep Trench Capacitor。研發進度上預計將於2022年推出基於N5工藝的SoIC封裝技術:

資料來源:臺積電3D SoIC技術開發進度,公開資料整理,阿爾法經濟研究

在今年8月22日舉行的年度Hot Chips大會上,臺積電Pathfinding for System Integration副總經理餘振華回顧了SoIC、InFO和CoWoS等臺積電先進封裝技術,並公佈了CoWoS封裝技術路線圖和SoIC晶片互連技術路線圖,預計將在2035年前或實現微米內SoIC互連,在1微米內臺積電的CoW可以直接整合成SoIC bonding工藝和SoC後端互連:

資料來源:SoIC晶片互連技術路線圖及Sub-微米CoW互連特點,公開資料整理,阿爾法經濟研究

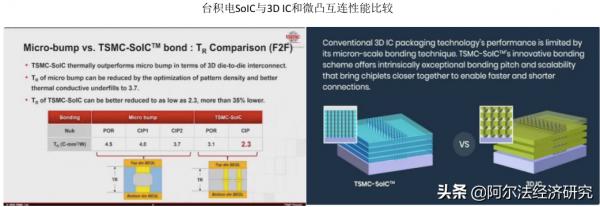

SoIC互連技術缺點是堆疊設計必須與其他晶片共同設計並且在最開始晶片設計方案就需要確定下來,而像英特爾EMIB此類微凸互連只需要後期把晶片連在一起,因此SoIC技術不利之處在於堆疊設計必須彼此協同設計。SoIC的熱電阻相比微凸連線降低了35%,因此雖然技術上相對來說更為複雜,但在熱阻上有很大的優勢,再加上較高的整合密度,這也是臺積電力推的原因:

資料來源:臺積電SoIC與3D IC和微凸點效能比較,公司官網整理,阿爾法經濟研究

在Hot Chips大會上餘振華提到,透過堆疊2D單元或3D層,SoIC除了能實現更多的記憶體容量和功能,還可以透過更換熱介面材料的方式讓晶片封裝熱阻不斷降低,3D堆疊中積累熱量的熱能瓶頸(Thermal Wall)也得以更好地解決。

多項新方案破除InFO技術瓶頸

臺積電後道兩大封裝技術InFO和CoWoS中,InFO即整合扇出晶圓級封裝技術,是一個具有高密度RDL和TIV特性、可實現高密度互連的2.5D整合技術,最初於2012年提出,2016年蘋果推出的A10採用InFO技術,蘋果也成為臺積電InFO第一個客戶。

InFO封裝技術允許晶片在SoC的標準平面之外扇出額外的連線增加IO介面,這意味著雖然晶片邏輯區域可以很小,但晶片要比邏輯電路更大以容納所有必需的引腳輸出連線。

資料來源:InFO與FLWLP、FOWLP差別對比,公開資料整理,阿爾法經濟研究

臺積電針對不同應用場景推出了InFO-PoP、InFO-oS和InFO-AiP等不同版本。InFO-PoP也就是InFO-R,是業界第一個3D晶圓級扇出封裝技術,具有高密度RDL和TIV,可將移動AP和DRAM封裝堆疊整合到移動應用中,在手機SoC中獲得應用。與FC-PoP相比,InFO-PoP由於沒有采用基板和C4凸點,因此具有更薄的外形和更好的電氣效能及熱效能。2018年臺積電推出InFO-oS,該技術用於並排封裝兩個晶片,晶片與晶片之間的互連為2微米,晶片之間間隙小於70微米:

資料來源:臺積電InFO-PoP與oS結構對比,公開資料整理,阿爾法經濟研究

InFO-oS即InFO-L於2018年量產,主要面向高效能計算HPC。InFO-oS允許在晶片和微凸點之間新增RDL,以便將多個晶片封裝在一起,提高更高密度來節省芯片面積。另外臺積電還透過在InFO-oS上加入LSI將晶片線寬和間距進一步縮小,也就是所謂的InFO-LSI技術:

資料來源:臺積電InFO-L/LSI技術,公開資料整理,阿爾法經濟研究

此外公司還正在研發InFO-I技術,其特點是使用區域性的矽互連將多個InFO晶片連線在一起。目前這項技術仍在研發中。

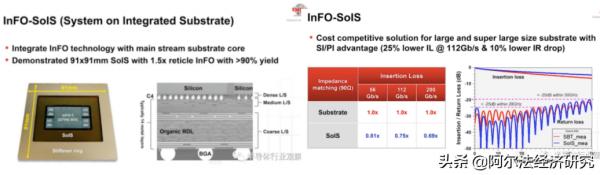

不過因為InFO-oS中使用了基板,隨著高速運算需求,基板面積與RDL層數會不斷增加,但基板的繩產量率與耗電逐漸成為產業發展的瓶頸。為此臺積電提出了InFO-SoIS方案,在其中透過整合超大尺寸InFO和整塊的基板來提供高良率和高可靠性以及高效能和高效率:

資料來源:臺積電InFO-SoIS技術特點,公開資料整理,阿爾法經濟研究

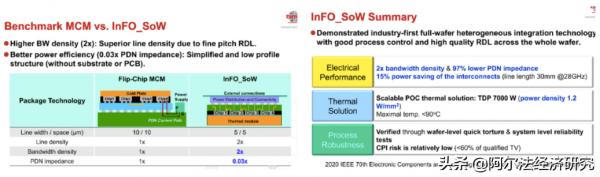

此外餘振華在Hot Chips會議上還提到另一種技術路線InFO-SoW,這是業界第一個全晶圓異質整合技術,尺寸較為緊湊,頻寬密度為FC MCM的2倍,PDN阻抗為FC MCM的3%,熱處理上因為其具有可擴充套件的POC熱處理方案,功率密度僅為1.2W每平方毫米,因此在頻寬密度、阻抗等方面具有較為顯著的優勢:

資料來源:臺積電InFO-SoW技術特點,公開資料整理,阿爾法經濟研究

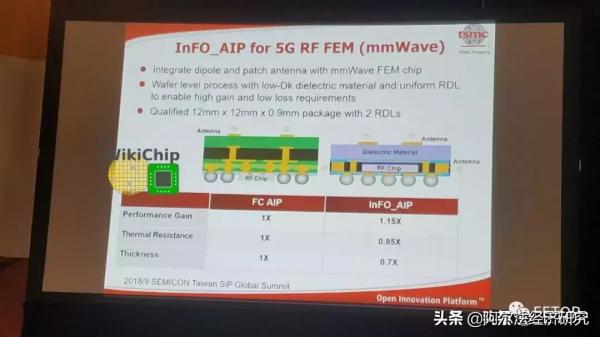

臺積電針對5G毫米波系統整合專門開發了InFO-AiP天線封裝技術,透過在RDL中實現插槽耦合貼片以及模塑化合物本身中的嵌入式RF晶片來降低晶片和天線之間因互連或鏈路導致的嚴重傳輸損耗。與FC AiP相比,InFO-AiP技術性能提高15%,熱阻和厚度分別降低15%和30%:

資料來源:臺積電InFO-AiP封裝技術特點,EETOP,阿爾法經濟研究

臺積電靠引以為傲的CoWoS要定義未來行業發展方向

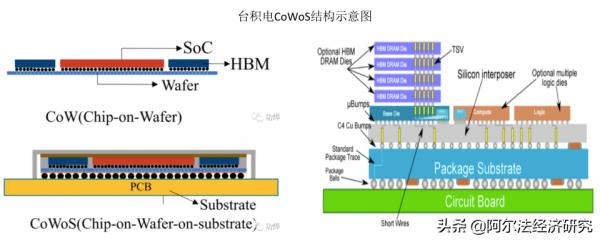

CoWoS是臺積電推出的一種2.5D封裝技術,先將晶片透過CoW封裝在晶圓上,然後再將CoW晶片與基板連線,整合成CoWoS。CoWoS可以把多顆晶片封裝在一起,透過Interposer互連,達到封裝體積小、功耗低和引腳少的效果,主要用於HBM。

從2012年臺積電首次釋出這項技術以來,公司會同客戶對這項技術進行多次強化,Interposer最大面積從約1070平方毫米擴充套件到約1700平方毫米,更大面積的Interposer可以封裝下更多的HBM模組,從而提供更高的記憶體頻寬。最新的CoWoS可以將6枚HBM封裝在一起,最大容量達到96GB,頻寬可高達2.7TB/s,比2016年提高了2.7倍:

資料來源:臺積電CoWoS技術結構,公開資料整理,阿爾法經濟研究

臺積電的CoWoS目前有CoWoS-S、CoWoS-R和CoWoS-L三個路線,其中CoWoS-S中的S代表矽中介層Interposer,目前已經更新到第四代,Interposer面積達到1700平方毫米。第五代CoWoS-S的Interposer面積達到2400平方毫米,由於採用新的熱介面材料和TSV技術,在導熱和互連效能上均有所提升,可用於chiplet、SoIC和第三代HBM3的整合。

根據臺積電CoWoS路線圖,公司將於今年晚些時候釋出第五代CoWoS-S技術,相比第三代電晶體數量增加20倍,Interposer面積提升3倍,可封裝8個128GB的HBM2記憶體和2顆大型SoC核心,將進一步推進高效能計算機HPC的發展:

CoWoS-S是以HBM+ASIC的組合實現,因此臺積電正以此為標準架構實施一個稱為CoWoS-S STAR的技術路線,將使客戶能在針對2/4/6HBM堆疊的特定設計協議內工作,最小化中介層的尺寸,還可以加快產品上市時間和提高良率。

CoWoS-L是另一種變種技術,使用了局部矽互連和RDL,這項技術與英特爾的EMIB技術類似,可將兩個矽晶片本地連線在一起。不過相比早已量產的EMIB,臺積電的CoWoS-L還處於預認證階段。CoWoS-L用於異質整合,可以利用InFO和CoWoS整合矽橋、被動元件等,透過RDL最佳化晶片效能:

資料來源:CoWoS-L技術及特點,公開資料整理,阿爾法經濟研究

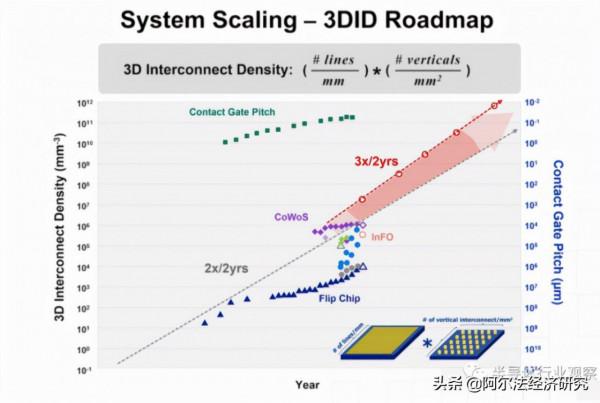

餘振華指出,晶片間內部連線密度的持續增加能否支援chiplet整合與異構整合技術的持續進步,為此臺積電提出了新的3D ID路線圖,提議3DID每兩年增加兩倍,以滿足功能和功耗的目的,這也被視為摩爾定律的2.0版本,試圖有效引領業界的研發:

資料來源:臺積電3DID技術路線圖,公開資料整理,阿爾法經濟研究

原創宣告:本文作者系阿爾法經濟研究原創,歡迎個人轉發,謝絕媒體、公眾號或網站未經授權轉載。

免責宣告:阿爾法經濟研究釋出的內容僅供參考,不構成任何投資建議。