在首次設想將可程式設計性嵌入ASIC裝置的概念幾十年後,許多行業趨勢已經融合,最終使其在經濟上可行。在供應方面,最根本的趨勢是掩模成本隨著每一代半導體工藝技術的發展而急劇上升,而電晶體(以及柵極)的成本則繼續下降。在需求方面,物聯網市場的出現及其相關的碎片化應用空間以及低成本和低功耗要求,催生了對具有低單位成本和低功耗的高度靈活的裝置的需求。這種需求已透過使用嵌入式開發處理器得到部分滿足,但其功耗與效能的權衡使其成為物聯網邊緣應用的不太理想的解決方案。讓我們更詳細地看一下這些趨勢中的每一個。

幾十年前,FPGA 門形式的可程式設計性對於 SoC 應用來說非常昂貴。 可靠的行業估計是,早期可程式設計門的成本是同等水平的“硬連線”ASIC 門的 50 倍。 同時,ASIC掩模成本比現在低了幾個數量級(幾萬美元而不是幾千萬美元),使得掩模旋轉的成本並不太可怕。 再加上早期可程式設計技術通常具有獨特(因此昂貴)的處理要求,並且總成本/收益分析總是顯示向 ASIC 新增可程式設計邏輯的顯著劣勢。

過去十年左右的消費半導體市場主要由高度標準化的移動裝置(如平板電腦和智慧手機)驅動。這些裝置通常共享具有通用架構的通用平臺,因此不需要為其提供服務的 SoC 具有高度的靈活性。物聯網作為消費電子產品的下一波增長浪潮的出現,伴隨著對更高裝置靈活性的需求,因為這些應用更加分散且難以預測,他們還要求嵌入式開發裝置具有較低的單位成本和功耗水平。沒有人願意花太多的錢,也沒有人願意為肯定會佔據我們共同未來的物聯網裝置群不斷更換電池。

可以說,SOC的“靈活性”問題在很大程度上已經透過嵌入式處理器解決了。這種方法確實創造了極其靈活的裝置,具有軟體可程式設計的高度理想屬性。然而,不幸的是,如果可能的話,處理器的功耗可能是基於硬體的解決方案的五到十倍。對於大多數物聯網應用來說,高功耗是一個大問題,尤其是那些處於網路邊緣的應用。

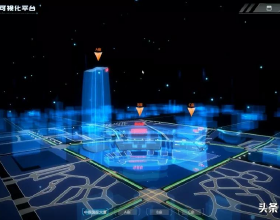

邏輯解決方案是嵌入式FPGA(eFPGA)技術。可程式設計邏輯電晶體和門的成本已經下降到可以將它們新增到SoC中而不需要顯著增加晶片尺寸的程度。事實上,pad限制裝置可以有效地免費獲得它們。具有硬體可程式設計性使嵌入式開發人員能夠滿足廣泛的物聯網應用需求,而無需為每個應用程式建立單獨的裝置。它還允許設計解決以前需要處理器(或更大的處理器)的問題,同時降低功耗,甚至可能提高效能。新興和/或快速發展的市場需求可以很容易地得到滿足,因此無需預測裝置的功能需求,而裝置只能每隔幾年進行一次經濟迭代。