SiC MOSFET溝槽結構將柵極埋入基體中形成垂直溝道,儘管其工藝複雜,單元一致性比平面結構差。但是,溝槽結構可以增加單元密度,沒有JFET效應,寄生電容更小,開關速度快,開關損耗非常低;而且,透過選取合適溝道晶面以及最佳化設計的結構,可以實現最佳的溝道遷移率,明顯降低導通電阻,因此,新一代SiC MOSFET主要研究和採用這種結構。

這種結構柵極溝槽底部氧化層的工作電場強度高,在高的反向偏置電壓下,此處成為器件最薄弱的環節。溝槽結構SiC MOSFET的技術演進方向,就是採用最佳化的內部結構,減小溝槽底部氧化層工作電場強度,本文列出了一些常見結構。

1、Rohm的雙溝槽結構

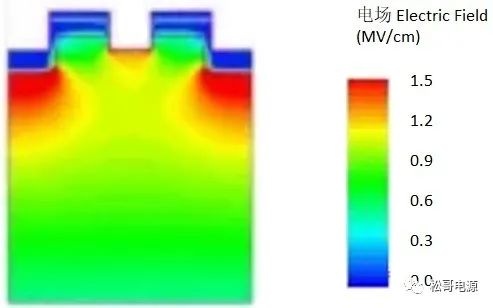

柵極溝槽底部氧化層外二側P-體區下移,下移P-體區和溝槽底部附近的N-區漂移層的PN接面,形成耗盡層,也就是空間電荷區,降低柵極溝槽底部氧化層內的工作電場強度,這是一種最為經典、實用的專利結構。

圖1 Rohm雙溝槽結構及電場分佈

2、Infineon非對稱溝槽結構

柵極溝槽底部氧化層外P-體區單側下移,半包裹柵極溝槽底部區域,下移P-體區和溝槽底部附近N-區漂移層的PN接面,形成耗盡層、也就是空間電荷區,降低柵極溝槽底部氧化層內的工作電場強度。

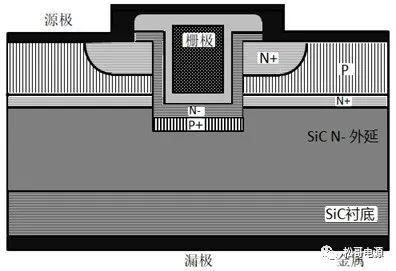

3、普渡大學Integral Oxide Protection綜合氧化保護結構

綜合氧化保護結構IOP改進地方有3部分:整個柵極溝槽氧化層外,包括底部和側壁,使用低摻雜薄層N-型SiC,把柵極氧化層隔開;柵極溝槽下部,再增加一層P+型SiC;P-體區和N-漂移層之間增加一層高摻雜N+型SiC。

器件處於反向偏置時,柵極溝槽下面新增PN接面形成空間電荷區,也就是耗盡層,可以對柵極氧化層起到遮蔽電場作用,將柵極氧化層內最大電場轉移到PN接面,減小柵極氧化層內的工作電場,甚至讓柵極氧化層電場減少到0,有效消除柵極氧化層被電場擊穿可能性。

柵極溝槽側壁薄層低摻雜N-型SiC,可以降低SiC-SiO 介面態對溝道電子散射作用,提高電子遷移率,降低器件導通電阻。器件導通時,P-體區和N-漂移層之間新增高摻雜N+型層,促進溝道電子進入漂移區後立即擴充套件,進一步降低導通電阻。

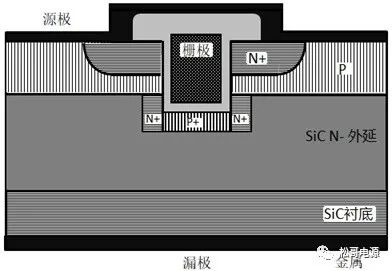

4、Mitsubishi溝槽結構

採用非對稱溝槽結構,柵極溝槽底部區域有3個結構:底部P+電場限制結構,側接地電場限制層(圖4中溝槽底部左側P區)、高濃度N+摻雜導電區(圖4中溝槽底部右側N+區)。柵極溝槽底部的P+電場限制結構和N-漂移層形成PN接面,PN接面的耗盡層、也就是空間電荷區,將加在柵極氧化層的電場強度降低到普通平面結構的水平,側接地電場限制層將電場限制層連線到源極,形成側接地,實現高速開關。高濃度摻雜導電區,降低電流通路的導通電阻。

其改進結構如圖5所示,溝槽底部區域變為2個結構:溝槽底部的P+電場限制結構和溝槽底部周圍的高濃度摻雜N+導電區(圖5中溝槽底部二側N+)。P+電場限制結構將加在柵極溝槽氧化層的電場強度降低,高濃度摻雜N+導電區降低電流通路的導通電阻。

5、Fuji Electric

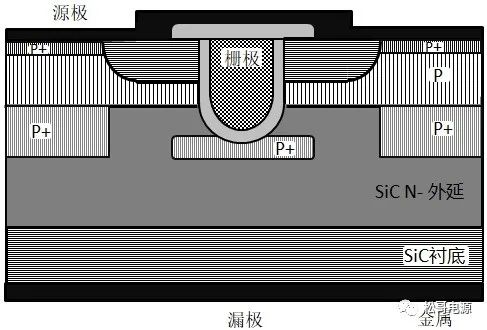

柵極溝槽二側的P-體區部分下移,使用高摻雜P+;柵極溝槽底部氧化層外,增加掩埋的P+浮島結構,和N-漂移層形成PN接面,PN接面的耗盡層、也就是空間電荷區,降低柵極溝槽底部氧化層內的工作電場強度。

6、日本住友/豐田

柵極溝槽二側P-體區部分下移,使用高摻雜P+,在溝槽底部氧化層外附近區域,下移P+區截面積變寬,延伸到柵極溝槽底部氧化層外附近區域,讓下移的P+區和柵極溝槽底部附近的N-漂移層形成PN接面,PN接面的耗盡層,降低柵極溝槽底部氧化層內的電場強度,溝槽採用V形結構。

7、日本Denso電裝

類似於住友的溝槽結構,只是改為U形溝槽。

總結:這些結構核心就是在柵極溝槽底部或柵極溝槽底部附近區域,增加P型結構,形成耗盡層(空間電荷區),從而,把柵極溝槽底部氧化層電場,部分轉移到耗盡層中,減小柵極溝槽底部的電場。