設計一款自動駕駛晶片挑戰Mobileye和英偉達是不是有點不自量力?未必,目前自動駕駛系統晶片即SoC設計大都是搭積木的方式,各種第三方IP就是積木,只要搭配得當,還是有可能挑戰Mobileye和英偉達的,關鍵不在於技術,而在於有持續不斷的巨量資金注入,這是一場馬拉松比賽,堅持到最後就是勝利。

Mobileye的優勢是軟硬一體,開發週期最短,開發成本最低,技術成熟穩定,缺點是產品同質化明顯,無法凸顯整車廠的特色。MIPS指令集導致其系統封閉,升級能力差,無法適應快速演進的感測器技術,特別是鐳射雷達的大量出現。英偉達的優勢是AI算力極其強大,留有足夠的算力冗餘,能適應各種演算法,也能滿足未來3-6年的演算法演變。GPU的浮點算力也很強大,算力冗餘足夠,視覺感知能力強。英偉達提供完整的軟體棧,系統也有點封閉,但算力很強大,整車廠還是能做出特色。缺點是GPU佔裸晶面積大,硬體成本居高不下。

實際自動駕駛雷聲大雨點小,在2017和2018年,眾多科技類企業或整車廠都信誓旦旦要在2020年或2021年推出L4級車,沒有方向盤和剎車踏板,最終都不了了之。2021年則是很多廠家推出號稱L3/L4的量產車,但年銷量都很難上千,究其原因主要是價效比太低,所謂L3/L4就是加強版的自適應巡航或堵車時的自動跟車,但代價卻很高。目前L3/L4的技術條件遠未成熟,未達到量產上路的地步,比如感知領域,突然出現的靜止目標,非標障礙物,嬰兒和小孩低矮目標探測與識別,光強度的迅速變化等挑戰,以及決策領域的允許加塞或不允許等。此外,基礎條件也不具備,如高精度地圖和定位,紅綠燈的V2X等。

未來10年內,L2+還是市場主流,至少佔到90%的市場。高AI算力在L2+領域沒有用武之地,所謂AI算力,只是卷積加速器,只是視覺分類的一個功能。遇上突然出現的靜止目標、非標障礙物、嬰兒和小孩低矮目標,即使再高的AI算力,還是要出事故,但硬體廠家的推波助瀾,讓消費者誤以為高算力就是高等級自動駕駛。

要提高安全性不是提高AI算力就能做到的,鐳射雷達或立體雙目能提供原生3D感知的感測器應用才能提高安全性,同時也要基於傳統可解釋可預測演算法才能提高安全性。深度學習是個黑盒子,無法預測結果,無法解釋,無法提高安全性。立體雙目技術門檻太高,只有賓士豐田大廠才玩得轉,這是內部培養了十幾年人才的成果。大部分企業都只能選擇鐳射雷達。

鐳射雷達對SoC運算資源的需求CPU就可以完成,避免使用高成本的GPU。

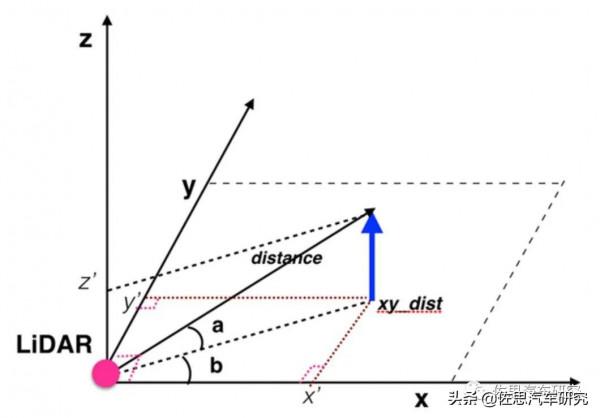

LiDAR透過鐳射反射可以測出與物體之間的距離distance,因為鐳射的垂直角度是固定的,記做a,這裡我們可以直接求出z軸座標為sin(a)*distance。由cos(a)*distance我們可以得到distance在xy平面的投影,記做xy_dist。LiDAR在記錄反射點距離的同時也會記錄下當前LiDAR轉動的水平角度b,根據簡單的集合轉換,可以得到該點的x軸座標和y軸座標分別為cos(b)*xy_dist和sin(b)*xy_dist。

Velodyne VLP-16的資料包

鐳射雷達的資料處理主要是兩部分,第一部分是座標變換,包括極座標到直角座標XYZ之間的變換,鐳射雷達座標系與車輛座標系的變換,這其中主要是三角函式變換。第二部分是點雲配準。去噪音等預處理可以看做點雲配準的一部分工作。

早期乘法運算和浮點運算資源奇缺,因此J. Volder於1959年提出了一種快速演算法,稱之為CORDIC(COordinateRotation DIgital Computer) 座標旋轉數字計算演算法,這個演算法只利用移位和加減運算,就能計算常用三角函式值,如Sin,Cos,Sinh,Cosh等函式。J. Walther於1974年在這種演算法的基礎上進一步改進,使其可以計算出多種超越函式,進一步擴充套件了Cordic 演算法的應用。因為Cordic 演算法只用了移位和加法,很容易用CPU來實現。Cordic演算法首先用於導航系統,使得向量的旋轉和定向運算不需要做查三角函式表、乘法、開方及反三角函式等複雜運算。

CORDIC用不斷的旋轉求出對應的正弦餘弦值,是一種近似求解法。旋轉的角度很講求,每次旋轉的角度必須使得正切值近似等於 1/(2^N)。旋轉的目的是讓Y軸趨近於0。把每次旋轉的角度累加,即得到旋轉的角度和即為正切值。比如Y軸旋轉45度,則值減小1/2,再旋轉26.56505°,再減少1/4,再旋轉角度14.03624º,再減少1/8,依次減少1/16,1/32......,最後Y軸的值無限小,趨近於0 。要避免浮點運算也很簡單,我們用256表示1度(即8位元)。這樣的話就可以精確到1/256=0.00390625度了,這對於大多數的情況都是足夠精確的了。256表示1度,那麼45度就是 45*256 = 115200。其他的度數以此類推。只取整數運算,避免了浮點運算。

第二部分運算量比較大的,也是程式設計師們比較關注的,一般三角函式計算座標變換都是鐳射雷達廠家提供SDK的。

說到點雲配準,就繞不開PCL庫。PCL庫源自ROS,即機器人作業系統,機器人系統經常用到鐳射雷達3D影像,為了減少重複開發,打通各個平臺,ROS推出了PCL庫。PCL(Point Cloud Library)是在吸收了前人點雲相關研究基礎上建立起來的大型跨平臺開源C++程式設計庫,它實現了大量點雲相關的通用演算法和高效資料結構,涉及到點雲獲取、濾波、分割、配準、檢索、特徵提取、識別、追蹤、曲面重建、視覺化等。支援多種作業系統平臺,可在Windows、Linux、Android、MacOSX、部分嵌入式實時系統上執行。如果說OpenCV是2D資訊獲取與處理的結晶,那麼PCL就在3D資訊獲取與處理上具有同等地位,PCL是BSD授權方式,可以免費進行商業和學術應用。其背後主要是慕尼黑大學(TUM - Technische Universität München)和斯坦福大學(Stanford University)。工業領域除了所有鐳射雷達廠家都支援PCL庫外,豐田和本田也是PCL庫的贊助者。

PCL庫建立於2013年,那個時代,CPU是最主要的運算資源,因此PCL庫針對CPU做了最佳化,PCL中的底層資料結構大量使用了SSE(可以看作是SIMID)最佳化。其大部分數學運算的實現是基於Eigen(一個開源的C++線性代數庫)。此外,PCL還提供了對OpenMP和英特爾執行緒構建模組(TBB)庫的支援,以實現多核並行化。快速最近鄰搜尋演算法的主幹是由FLANN提供(一個執行快速近似最近鄰搜尋的庫)。PCL中的所有模組和演算法均透過使用Boost共享指標的傳遞資料,因此避免重新複製系統中已經存在的資料。

點雲配準最常用的兩種方法一個是迭代最近點演算法ICP (Iterative Closest Point),KD樹可看做是ICP的高維版,一個是正態分佈變換NDT (Normal Distribution Transform)。這兩種演算法自然都在PCL庫裡。英特爾則在2020年推出類似PCL庫的Open3D開源庫,不用說,自然也有對CPU的最佳化。

現在讓我們再回到自動駕駛晶片,要應對不斷增加解析度的鐳射雷達,就要增強CPU算力,CPU的裸晶面積一般遠小於GPU,這就意味著CPU價效比更高。考慮到晶片的設計週期與應用量產週期有2-3年,因此效能要儘可能地強大,同時為了保持足夠的開放性,ARM架構是必須使用的。

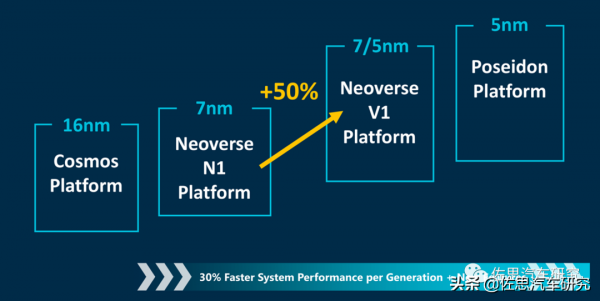

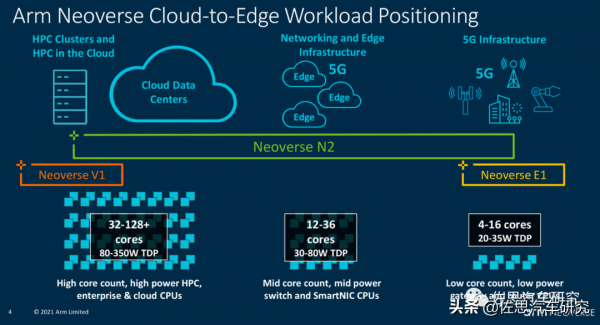

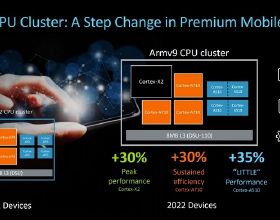

ARM在2019年3月針對伺服器HPC市場推出Neoverse平臺,按照計劃最初是Ares,即希臘神話裡的戰神,2020年是Zeus,即希臘神話中的宙斯,2022年是Poseidon。V1是ARM目前算力最強的CPU架構。

考慮到臺積電的產能緊張,價格高昂,即便是特斯拉這樣的知名客戶,也被臺積電拒之門外,因為特斯拉的量太低了,臺積電的資源都給大客戶了,小客戶的排期遙遙無期。從價效比和供應鏈的角度,三星是唯一選擇,三星產能充足,價格也遠低於臺積電,缺點是5奈米工藝不夠成熟,因此只能選擇7奈米的V1。

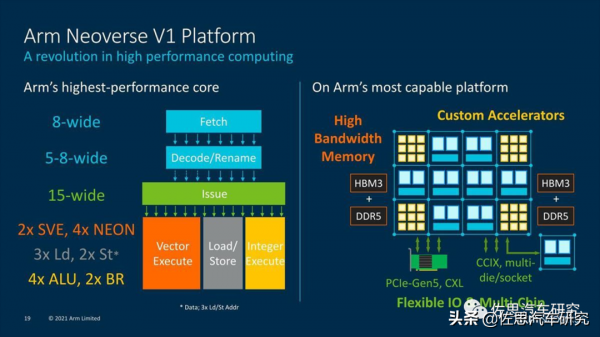

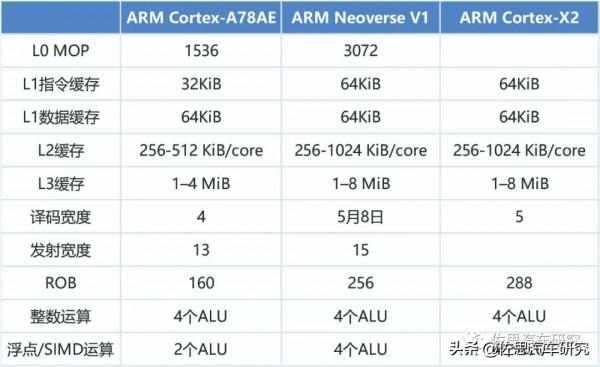

為什麼說V1是最強的?

影響CPU算力最關鍵的引數是Decode Wide譯碼寬度,譯碼寬度可簡單等同於每週期指令數量即IPC,即每個週期完成多少個指令。

譯碼寬度的增加是非常困難的,不是想多少就多少的,簡單來說每增加一位寬度,系統複雜度會提高15%左右,裸晶面積也就是成本會增加15-20%左右。如果簡單地增加譯碼寬度,那麼成本也會增加,廠家就缺乏更新的動力,所以ARM的做法是配合臺積電和三星的先進工藝,利用電晶體密度的提升來減少裸晶面積降低成本,因此ARM的每一次譯碼寬度升級都需要先進製造工藝的配合,否則成本增加比較多。同時ARM也從商業角度考慮,每年小升級一次,年年都有提升空間。8位寬度是目前的極限,蘋果一次到位使用8位寬度,缺點是必須使用臺積電最先進的製造工藝。

此外,RISC和CISC還有區別,CISC增加寬度更難,但CISC的1位寬度基本可頂RISC的1.2-1.5位。英特爾是有實力壓制蘋果的,就是製造工藝不如臺積電。CISC指令的長度不固定,RISC則是固定的。因為長度固定,可以分割為8個並行指令進入8個解碼器,但CISC就不能,它不知道指令的長度。因此CISC的分支預測器比RISC要複雜很多,當然目前RISC也有長度可變的指令。遇到有些長指令,CISC可以一次完成,RISC因為長度固定,就像公交車站,一定要在某站停留一下,肯定不如CISC快。也就是說,RISC一定要跟指令集,作業系統做最佳化,RISC是以軟體為核心,針對某些特定軟體做的硬體,而CISC相反,他以硬體為核心,針對所有型別的軟體開發的。

V1的寬度是可變的,最高8位

ARM Neoverse V1的微架構

除了譯碼寬度,後端的分佈和發射(Dispatch與Issue)寬度和ALU也要跟得上,否則前端很忙,後端很閒,也是沒用,通常提升方法是增加發射寬度。分佈方面,ARM Cortex-A77是10位,V1是10位,蘋果M1的大核Firestorm據說是13位,三星貓鼬M4/M5是12位。不過V1的發射單元比較多,有15位。後端的運算單元ALU也比較多,有8個,4個整數,4個浮點或SIMD。

V1是針對HPC開發的,推薦32核以上配置,但車載肯定不能這樣做,功耗太高,12核V1足夠,算力基本上能與16核的ARM Cortex-A78AE相當,甚至還要更高。浮點運算也不弱。

Neoverse V1的機器學習效能和浮點運算效能也很強。

機器學習效能,V1是N1的4倍,浮點運算效能是N1的2倍,典型的N1是華為的鯤鵬系列伺服器CPU,也就是華為稱之為泰山V110核心。

ARM最近引入2代SVE,NEON指令集是ARM64架構的單指令多資料流(SIMD)的標準實現。SVE(可擴充套件向量指令Scalable Vector Extension)是針對高效能計算(HPC)和機器學習等領域開發的一套全新的向量指令集,它是下一代SIMD指令集實現,而不是NEON指令集的簡單擴充套件。SVE指令集中有很多概念與NEON指令集類似,例如向量、通道、資料元素等。SVE指令集也提出了一個全新的概念:可變向量長度程式設計模型(VectorLength Agnostic,VLA)。

傳統的SIMD指令集採用固定大小的向量暫存器,例如NEON指令集採用固定的128位長度的向量暫存器。而支援VLA程式設計模型的SVE指令集則支援可變長度的向量暫存器。這樣允許晶片設計者根據負載和成本來選擇一個合適的向量長度。SVE指令集的向量暫存器的長度最小支援128位,最大可以支援2048位,以128位為增量。SVE設計確保同一個應用程式可以在支援不同向量長度的SVE指令機器上執行,而不需要重新編譯程式碼,這是VLA程式設計模型的精髓。

SVE指令集是在A64指令集的基礎上新增的一組指令集,而SVE2是在ARMv9架構上釋出的,它是SVE指令集的一個超集和擴充。SVE指令集包含了幾百條指令,它們可以分成如下幾大類:載入儲存指令以及預取指令,向量移動指令,整數運算指令,位操作指令,浮點數運算指令,預測操作指令,資料元素操作指令。

簡單地說,針對8位精度,如果SVE用理想狀態下的2048位指令,那麼相當於同時256個核平行計算,如果是16位精度就是128核。如果處理器有12核,那麼做深度學習時可近似為256*12=3072個核心執行,與GPU相差無幾。當然如此寬的資料操作編譯器自動向量化無能為力,為難開發者手動彙編也不好做。並且需要足夠的快取和暫存器數量來配合,成本會暴增。不過256或512位還是問題不大,英特爾的AVX512指令就是如此。一般推理用的就是8位整數精度,512位就是近似64核。簡單算一下,假設是512位寬,12核心,那麼就是64*12=768個核心,執行頻率2GHz,理想狀態下就是768*2=1526GOPs的算力。

選擇CPU後就是選擇GPU。GPU實際上就是針對並行資料的浮點運算器,也就是針對計算機視覺的,鐳射雷達的大量使用有助於降低對視覺的依賴,而計算機視覺是最耗費浮點算力的,鐳射雷達的大量使用是未來可以確定的事實,加上GPU最耗費成本,且很難做得過英偉達,因此不需要太高。

選擇ARM的MALI G710,16核配置650MHz下可以獲得1174GFLOPS的算力。

G710可能是ARM最成功的GPU架構。

與英偉達桌面級GPU比,ARM的架構差異比較大。ARM採用大核設計,一般寫為MALI G710 MPX或MCX,X代表核心數,MALI的核心就是渲染核即Shader Core,可以近似於英偉達的SM流多處理器。渲染核裡有執行引擎,可以算是CPU領域的ALU。

MALI G710渲染核

早期ARM是SIMD設計,近期變為GPU常用的SIMT。G710的執行引擎比G77翻倍,有兩個執行引擎,每個執行引擎包含兩個簇,執行16位寬的執行緒,等於是64個ALU,G710支援7-16核設計,也就是最高1024個ALU。

MALIG710執行引擎

G710的執行核,前端沒有透露具體資訊,應該和G77一樣,是64個warp或1024個執行緒。每個處理單元都有三個ALU:FMA(混合的乘積累加計算)和CVT(Convert)單元是16-wide,而SFU(特殊功能單元)是4-wide。每個FMA每週期可以做16次運算,運算資料精度為FP32,換成FP16就是32次,8位整數INT8就是64次,像英偉達的桌面級GPU,FP16和FP32是分開計算的,也就是說可以同時計算,但移動級的MALI不需要這樣設計。Convert單元處理基本整數操作和自然型別轉換操作,並充當分支埠。

ARMMALI GPU CSF

G710最大的變化,添加了CSF。G710首次把Mali的jobmanager換成了所謂的Command Stream Frontend。這個CSF負責處理排程和draw call,CSF這個模組由CPU、HW和韌體構成。Arm表示,HW本身是全新設計的;而韌體層的引入,能夠針對一些比較複雜的圖形負載提供更具彈性的效能,而且能夠減少驅動開銷、提升效率;對諸如Vulkan等API提供更簡捷的支援等。韌體處理來自host的請求和通知,負責硬體資源排程,減少諸如protected mode進出的開銷,還能透過指令模擬來提供硬體原本不具備的特性。

ARM MALI系列GPU最被人詬病的就是draw call開銷太大,實際效能與理論效能差別很大,特別是玩3D遊戲時,此時CPU和GPU都很費資源,CPU優先處理內部需求,對於GPU的draw call處理不夠及時,導致幀率下降。

接下來是AI加速器,計算機視覺依賴AI加速器,但鐳射雷達不需要太多AI加速。傳統AI加速器靠堆砌MAC數量,數量越多,理論算力越強,非常簡單粗暴,缺點是成本高,效率低。特別是效率低下,雖然理論算力數字非常漂亮,做到幾百TOPS很容易,但實際使用中,記憶體牆的瓶頸,算力會大打折扣,還有演算法模型的適配性,有時候只有理論算力的10%,而車載晶片受限於成本,又不可能使用高頻寬HBM記憶體。

典型的AI加速器其核心是基於流水線的指令並行,即當前處理單元的結果不寫回快取,而直接作為下一級處理單元的輸入,取代了當前處理單元結果回寫和下一處理單元資料讀取的儲存器訪問。這就是所謂脈動陣列,基本上AI加速器都是如此。這實際上兩維的超寬SIMD,一個橫向,一個縱向,2個維度最大化複用資料,從上傳下PE(計算單元)間複用權重和partial sum,從左到左傳PE間複用輸入特徵圖。從相鄰PE拿資料,前後門傳一下就行,不需要去共享大型SRAM取資料,省掉大量定址邏輯,資料能耗更低。控制邏輯艱難,佈線簡單,裸晶面積小,功耗低,頻率可以做到2-3GHz,同時架構易擴充套件,常見的有4096和8192兩種。有些如華為和英偉達,做成了3維,實際和2維度相差不大,最後那一維是前兩維的延伸,本質上還是兩維。

這種架構的缺點就是除非資料完全符合脈動陣列的規模,否則延遲明顯,如TPU的256x256脈動陣列,當遇到FC層輸入輸出節點少、1x1的卷積核等情況,還是要空轉256個週期才能有第一個計算結果,效率急速降低,解決辦法很簡單,軟硬一體,確保讓陣列都能滿負荷運轉。不過嘛,這就徹底封閉了,等於把靈魂都給晶片廠家了。

卷積的運算也有兩種,一種是脈動陣列最合適的矩陣乘加累積,另一種是滑動視窗,轉換成矩陣乘的好處之一就是方便支援各種奇奇怪怪的卷積,在轉換階段就做了dialation擴張、stride步長、deform變形、pad、非對稱卷積核等處理,但會多幾個資料轉換和額外的記憶體讀寫。直接滑窗可能不需要變形和額外記憶體讀寫,但最佳化起來卷積方式相對受限,如果在卷積階段調整步長或dialation等邏輯,會引起流水線中斷,降低效率。不過似乎可以用VLIW指令做對應約束。

除此之外,AI加速器還是標準的馮諾依曼架構,資料和程式指令共用一個匯流排,雖然可以分開儲存,像今天大多數CPU的L1快取都是指令和資料分開儲存,但定址匯流排還是共用的,仍然是標準的馮諾依曼架構,這在AI加速器上非常不合適,AI加速器有著天量的資料存取,消耗大量時間,產生大量功耗,即便是脈動陣列資料大量複用,但是指令和資料還是共用匯流排,資料還是要頻繁地讀出和寫入,這就是儲存牆問題。解決辦法有多種,一種是增加SRAM容量,SRAM速度最快,還在Die內部,物理距離最近,但成本會暴增,除了訓練用,推理階段絕對不會有人用。HBM退而求其次的辦法,是一種解決辦法,HBM頻寬高,容量遠大於SRAM,且與計算單元物理距離很近,在每次計算的兩個值中,一個是權值Weight,一個是輸入Activation。如果有足夠大的片上快取,結合適當的位寬壓縮方法,將所有Weight都快取在片上,每次僅輸入Activation,就可以在最佳化資料複用之前就將頻寬減半。不過HBM必須用3D封裝或者說Chiplet,基本上就只有臺積電一家能做,且價格高昂,車載晶片用不起。未來如果持續縮小權重模型,使用HBM量降低,或許會出現車載的HBM。

最合適的解決辦法是哈佛架構,哈佛架構可以一定程度上減少儲存牆的問題,它的指令和資料是不同的匯流排,讀取指令同時也可以讀取資料,沒有等待的間隙。DSP是典型的哈佛架構。缺點是通常要配合VLIW,編譯器寫起來很麻煩,再有就是DSP無法做到多核,算力難以大幅度提升。

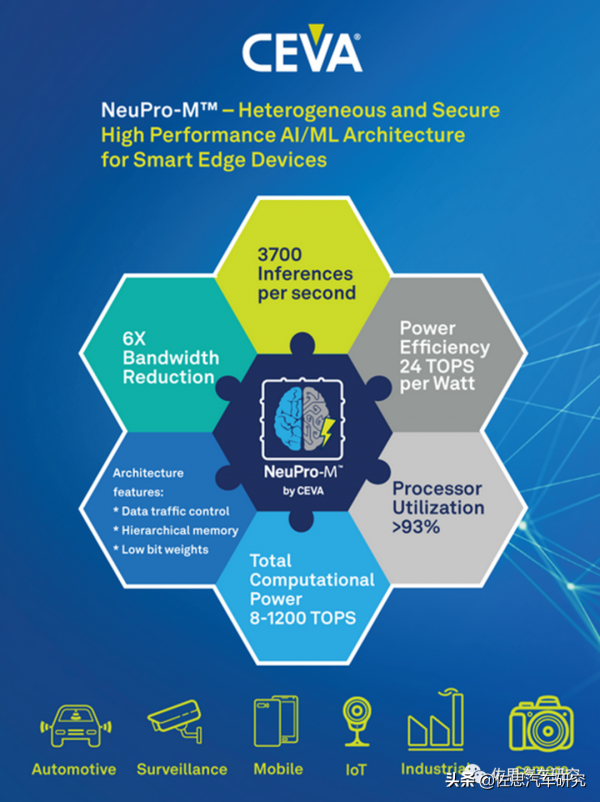

本文這款晶片更多考慮價效比、高效率以及對鐳射雷達的支援,因此不需要太高的AI算力,選擇CEVA的NeuPro M。用於車載AI加速的DSP IP供應商不少,如新思科技的DesignWare ARC處理器系列,Cadence的Tensilica Vision Q7,VeriSilicon(芯原微電子)的Vivante Vision IP,Imagination的NNA。DSPIP最大的還是CEVA,並且第一大汽車邏輯晶片廠家瑞薩在其下一代自動駕駛SoC中就有采用CEVA的DSP IP,極有可能就是NeuProM。

2022年1月初CES大展期間,CEVA推出第三代AI加速器IP,即NeuPro-M,最高算力達1200TOPS,且每瓦就可達到24TOPS算力,效率大約是高通AI100的2倍,英偉達Orin的2.5倍,特斯拉FSD的4-5倍。

針對汽車市場,CEVA提供NeuPro-M核心及其CEVA深度神經網路 (CDNN)深度學習編譯器和軟體工具包,不僅符合汽車ISO26262 ASIL-B功能安全標準,並滿足嚴格的質量保證標準IATF16949和 ASPICE要求。

NeuPro-M內部框架圖

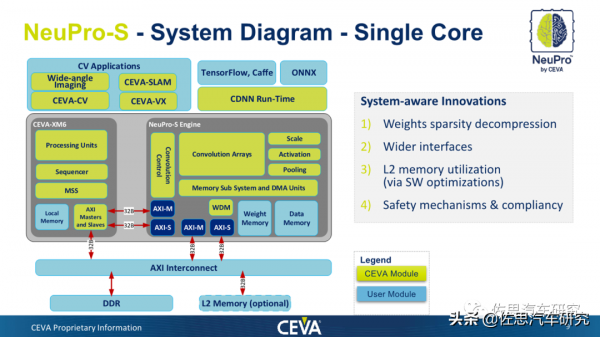

第二代產品NeuPro-S的框架圖

上圖為第二代產品NeuPro-S的框架圖,其實際是CEVA-XM6 DSP與NeuPro-S引擎的複合體,雖然NeuPro-M內部框架圖未再提及XM6,但看AXI主從分佈,XM6應該只是換了個名字叫NPM Common子系統。NeuPro-S引擎有點類似於一個脈動陣列的AI加速器,以NeuPro-S 4000擁有4096個整數8位元精度MAC單元,上圖為其單核框架圖。NeuPro-M也是4096個MAC,不過精度從2位整數到16位浮點都有。NeuPro-M 架構中創新功能,同時使用 Winograd變換正交機制、Sparsity引擎和低解析度 4x4位啟用,可將網路(如Resnet50和YoloV3)的迴圈次數減少三倍以上。

XM6的內部框架

NeuPro–M系列處理器初始包含以下預配置核心:• NPM11 –單個NeuPro-M引擎,在 1.25GHz下算力高達20 TOPS,• NPM18 – 8 個NeuPro-M 引擎,在1.25GHz下算力高達160 TOPS,這裡的TOPS對應都應該是8位元整數位精度。估計製造工藝是7奈米,5奈米執行頻率可以再提高,本設計中用單核NPM11就足夠,功耗低於1瓦,也更容易過車規,成本也比較低。

子系統不多,特別是AI加速器只是單核,因此片上網路NoC也可以不用,匯流排就足夠,ARM的CMN700就夠用。

設計一款效能足以挑戰英偉達Orin和Mobileye EyeQ6H的晶片不是什麼難事,最大的問題是資金從哪來,供應鏈如何確保。至於配套的軟體部分,只要捨得花錢招人,不是什麼難事。

報告訂購及合作諮詢私信小編

佐思 2022年研究報告撰寫計劃

智慧網聯汽車產業鏈全景圖(2021年12月版)

|

主機廠自動駕駛 |

汽車視覺(上) |

高精度地圖 |

|

商用車自動駕駛 |

汽車視覺(下) |

高精度定位 |

|

低速自動駕駛 |

汽車模擬(上) |

OEM資訊保安 |

|

ADAS與自動駕駛Tier1 |

汽車模擬(下) |

汽車閘道器 |

|

汽車與域控制器 |

毫米波雷達 |

APA與AVP |

|

域控制器排名分析 |

車用鐳射雷達 |

駕駛員監測 |

|

鐳射和毫米波雷達排名 |

車用超聲波雷達 |

紅外夜視 |

|

E/E架構 |

Radar拆解 |

車載語音 |

|

汽車分時租賃 |

充電基礎設施 |

人機互動 |

|

共享出行及自動駕駛 |

汽車電機控制器 |

L4自動駕駛 |

|

EV熱管理系統 |

混合動力報告 |

L2自動駕駛 |

|

汽車功率電子 |

汽車PCB研究 |

燃料電池 |

|

無線通訊模組 |

汽車IGBT |

汽車OS研究 |

|

汽車5G |

汽車線束 |

線控底盤 |

|

合資品牌車聯網 |

V2X和車路協同 |

轉向系統 |

|

自主品牌車聯網 |

路側智慧感知 |

模組化報告 |

|

自主品牌ADAS研究 |

商用車車聯網 |

商用車ADAS |

|

汽車多模態互動 |

汽車智慧座艙 |

車載顯示 |

|

Tier1智慧座艙(上) |

座艙多屏與聯屏 |

智慧後視鏡 |

|

Tier1智慧座艙(下) |

智慧座艙設計 |

汽車照明 |

|

座艙SOC |

汽車VCU研究 |

汽車座椅 |

|

汽車數字鑰匙 |

TSP廠商及產品 |

HUD行業研究 |

|

汽車雲服務平臺 |

OTA研究 |

汽車MCU研究 |

|

AUTOSAR研究 |

智慧停車研究 |

感測器晶片 |

|

軟體定義汽車 |

Waymo智慧網聯佈局 |

ADAS/AD主控晶片 |

|

T-Box市場研究 |

自動駕駛法規 |

ADAS資料年報 |

|

T-Box排名分析 |

智慧網聯和自動駕駛基地 |

汽車鎂合金壓鑄 |

|

乘用車攝像頭季報 |

智慧汽車個性化 |

飛行汽車 |

|

專用車自動駕駛 |

農機自動駕駛 |

礦山自動駕駛 |

|

港口自動駕駛 |

自動駕駛重卡 |

無人接駁車 |

|

儀表和中控顯示 |

車載DMS |

合資品牌ADAS |

|

800V高壓平臺 |

本土品牌環視 |

汽車無線模組 |

「佐思研究月報」

ADAS/智慧汽車月報 | 汽車座艙電子月報 | 汽車視覺和汽車雷達月報 | 電池、電機、電控月報 | 車載資訊系統月報 | 乘用車ACC資料月報 | 前視資料月報 | HUD月報 | AEB月報 | APA資料月報 | LKS資料月報 | 前雷達資料月報