選自 Medium

作者:Adi Fuchs

機器之心編譯

機器之心編輯部

在上一篇文章中,前蘋果工程師、普林斯頓大學博士 Adi Fuchs 解釋了 AI 加速器誕生的動機。在這篇文章中,我們將跟著作者的思路回顧一下處理器的整個發展歷程,看看 AI 加速器為什麼能成為行業焦點。

這是本系列部落格的第二篇,我們來到了整個系列的關鍵所在。在為新公司或新專案做推介時,風投資本家或高管經常會問一個基本問題:「為什麼是現在?」

為了回答這個問題,我們需要簡單回顧一下處理器的發展歷史,看看近些年這一領域發生了哪些重大變化。

處理器是什麼?

簡而言之,處理器是計算機系統中負責實際數字計算的部分。它接收使用者輸入資料(用數值表示),並根據使用者的請求生成新的資料,即執行一組使用者希望的算術運算。處理器使用其算術單元來生成計算結果,這意味著執行程式。

20 世紀 80 年代,處理器在個人電腦中被商品化。它們逐漸成為我們日常生活中不可或缺的一部分,膝上型電腦、手機和連線數十億雲和資料中心使用者的全球基礎設施計算結構中都有它們的身影。隨著計算密集型應用的日益普及和大量新使用者資料的出現,當代計算系統必須滿足對處理能力不斷增長的需求。因此,我們總是需要更好的處理器。長期以來,「更好」意味著「更快」,但現在也可以是「更高效」,即花同樣的時間,但使用的能源更少,碳足跡更少。

處理器進化史

計算機系統的進化是人類最傑出的工程成就之一。我們花了大約 50 年的時間達到了這樣一種高度:一個人口袋裡的普通智慧手機擁有的計算能力是阿波羅登月任務中用到的房間大小的計算機的 100 萬倍。這一演變的關鍵在於半導體行業,以及它如何改進處理器的速度、功率和成本。

英特爾 4004:第一款商用微處理器,釋出於 1971 年。

處理器是由被稱為「電晶體」的電子元件組成的。電晶體是邏輯開關,用作從原始邏輯函式(如與、或、非)到複雜算術(浮點加法、正弦函式)、儲存器(如 ROM、DRAM)等所有東西的構建模組。這些年來,電晶體一直在不斷縮小。

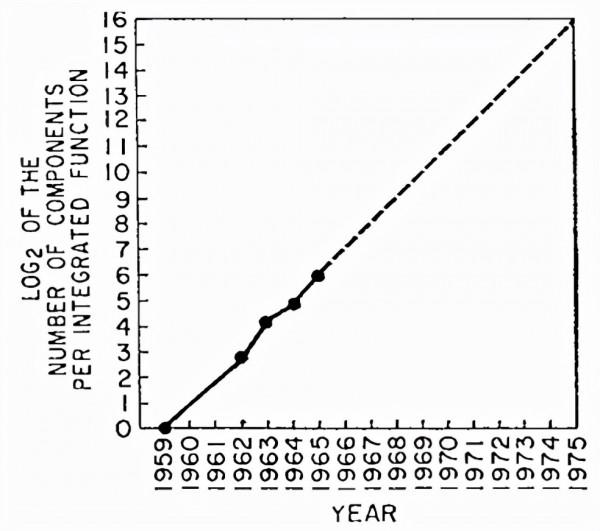

1965 年,戈登 · 摩爾發現,積體電路中的電晶體數量每年翻一番(後來更新為每 18-24 個月)。他預計這一趨勢將持續至少十年。雖然有人認為,這與其說是一個「定律」,不如說是一個「行業趨勢」,但它確實持續了大約 50 年,是歷史上持續時間最長的人為趨勢之一。

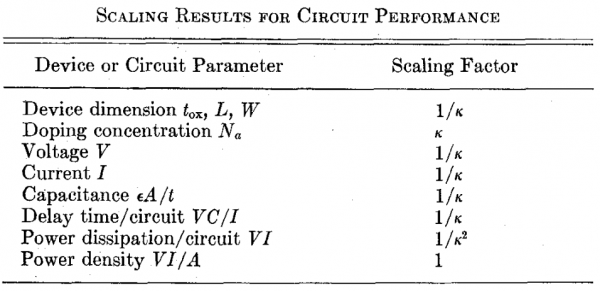

電晶體縮放的電學特性。

但除了摩爾定律,還有一條不那麼有名但同樣重要的定律。它被稱為「登納德縮放比例定律」,由羅伯特 · 登納德在 1974 年提出。雖然摩爾定律預測電晶體將逐年縮小,但登納德問道:「除了能夠在單個晶片上安裝更多電晶體之外,擁有更小的電晶體還有什麼實際好處?」他的觀察結果是,當電晶體以 k 為倍數縮小時,電流也會降低。此外,由於電子移動的距離更小,我們最終得到的電晶體快了 k 倍,最重要的是——它的功率下降到 1/k^2。因此,總的來說,我們可以多裝 k^2 個電晶體,邏輯函式將快大約 k 倍,但晶片的功耗不會增加。

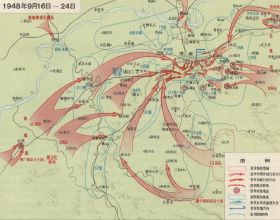

處理器發展第一階段:頻率時代(1970-2000 年代)

微處理器頻率速率的演變。

早期,微處理器行業主要集中在 CPU 上,因為 CPU 是當時計算機系統的主力。微處理器廠商充分利用了縮放定律。具體來說,他們的目標是提高 CPU 的頻率,因為更快的電晶體使處理器能夠以更高的速率執行相同的計算(更高的頻率 = 每秒更多的計算)。這是一種有些簡單的看待事物的方式;處理器有很多架構創新,但最終,在早期,頻率對效能有很大貢獻,從英特爾 4004 的 0.5MHz、486 的 50MHz、奔騰的 500MHz 到奔騰 4 系列的 3–4GHz。

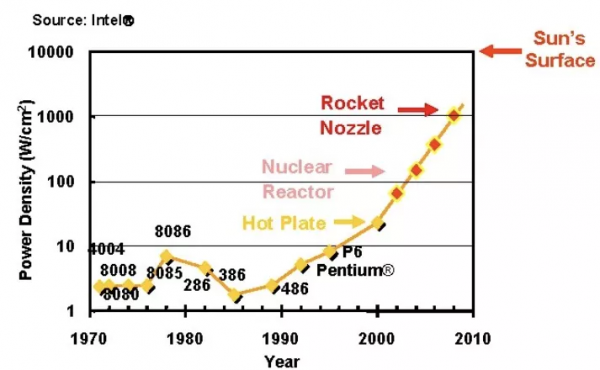

功率密度的演變。

大約在 2000 年,登納德縮放比例定律開始崩潰。具體來說,隨著頻率的提升,電壓停止以相同的速率下降,功率密度速率也是如此。如果這種趨勢持續下去,晶片發熱問題將不容忽視。然而,強大的散熱方案還不成熟。因此,供應商無法繼續依靠提高 CPU 頻率來獲得更高的效能,需要想想其他出路。

處理器發展第二階段:多核時代(2000 年代 - 2010 年代中期)

停滯不前的 CPU 頻率意味著提高單個應用的速度變得非常困難,因為單個應用是以連續指令流的形式編寫的。但是,正如摩爾定律所說的那樣,每過 18 個月,我們晶片中的電晶體就會變為原來的兩倍。因此,這次的解決方案不是加快單個處理器的速度,而是將晶片分成多個相同的處理核心,每個核心執行其指令流。

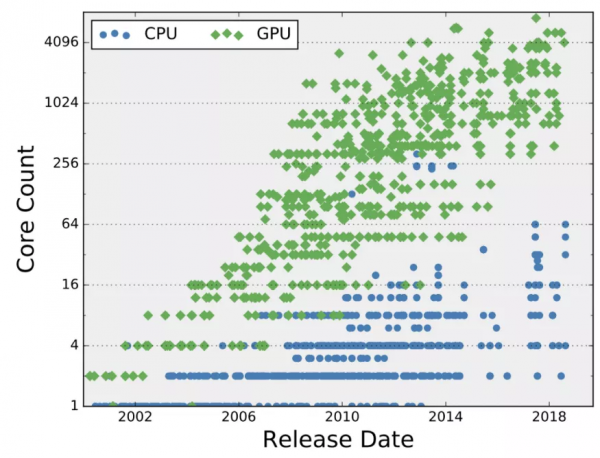

CPU 和 GPU 核數的演化。

對於 CPU 來說,擁有多個核心是很自然的,因為它已經在併發執行多個獨立的任務,比如你的網際網路瀏覽器、文字處理器和聲音播放器(更準確地說,作業系統在建立這種併發執行的抽象方面做得很好)。因此,一個應用可以在一個核心上執行,而另一個應用可以在另一個核心上執行。透過這種實踐,多核晶片可以在給定的時間內執行更多的任務。然而,為了加快單個程式的速度,程式設計師需要將其並行化,這意味著將原始程式的指令流分解成多個指令「子流」或「執行緒」。簡單地說,一組執行緒可以以任何順序在多個核心上併發執行,沒有任何一個執行緒會干擾另一個執行緒的執行。這種實踐被稱為「多執行緒程式設計」,是單個程式從多核執行中獲得性能提升的最普遍方式。

多核執行的一種常見形式是在 GPU 中。雖然 CPU 由少量快速和複雜的核心組成,但 GPU 依賴大量更簡單的核心。通常來講,GPU 側重於圖形應用,因為圖形影象(例如影片中的影象)由數千個畫素組成,可以透過一系列簡單且預先確定的計算來獨立處理。從概念上來說,每個畫素可以被分配一個執行緒,並執行一個簡單的「迷你程式」來計算其行為(如顏色和亮度級別)。高度的畫素級並行使得開發數千個處理核心變得很自然。因此,在下一輪處理器進化中,CPU 和 GPU 供應商沒有加快單個任務的速度,而是利用摩爾定律來增加核心數量,因為他們仍然能夠在單個晶片上獲得和使用更多的電晶體。

不幸的是,到了 2010 年前後,事情變得更加複雜:登納德縮放比例定律走到了盡頭,因為電晶體的電壓接近物理極限,無法繼續縮小。雖然以前可以在保持相同功率預算的情況下增加電晶體數量,但電晶體數量翻倍意味著功耗也翻倍。登納德縮放比例定律的消亡意味著當代晶片將遭遇「利用牆(utilization wall)」。此時,我們的晶片上有多少電晶體並不重要——只要有功耗限制(受晶片冷卻能力的限制),我們就不能利用晶片中超過給定部分的電晶體。晶片的其餘部分必須斷電,這種現象也被稱為「暗矽」。

處理器發展第三階段:加速器時代(2010 年代至今)

暗矽本質上是「摩爾定律終結」的大預演——對處理器製造商來說,時代變得具有挑戰性。一方面,計算需求飛速增長:智慧手機變得無處不在,而且擁有強大的計算能力,雲伺服器需要處理越來越多的服務,「最糟糕的是」——人工智慧重新登上歷史舞臺,並以驚人的速度吞噬計算資源。另一方面,在這個不幸的時代,暗矽成為電晶體晶片發展的障礙。因此,當我們比以往任何時候都更需要提高處理能力時,這件事卻變得以往任何時候都更加困難。

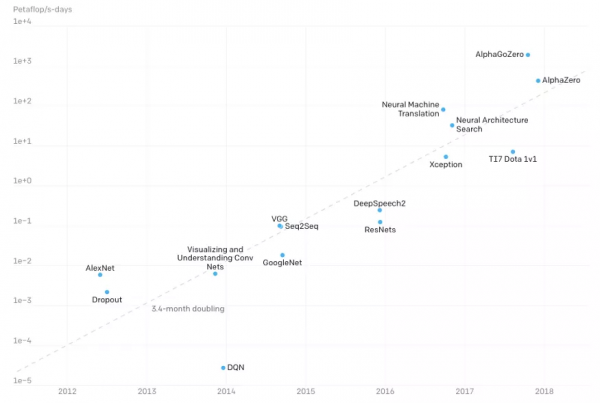

訓練 SOTA AI 模型所需的計算量。

自從新一代晶片被暗矽束縛以來,計算機行業就開始把精力放到了硬體加速器上。他們的想法是:如果不能再增加電晶體,那就好好利用現有的電晶體吧。具體怎麼做呢?答案是:專門化。

傳統的 CPU 被設計成通用的。它們使用相同的硬體結構來執行我們所有應用(作業系統、文字處理器、計算器、網際網路瀏覽器、電子郵件客戶端、媒體播放器等)的程式碼。這些硬體結構需要支援大量的邏輯操作,並捕獲許多可能的模式和程式誘發的行為。這相當於硬體可用性很好,但效率相當低。如果我們只專注於某些應用,我們就可以縮小問題領域,進而從晶片中去除大量的結構冗餘。

通用 CPU vs. 面向特定應用的加速器。

加速器是專門面向特定應用或領域的晶片,也就是說,它們不會執行所有應用(例如不執行作業系統),而是在硬體設計層面就考慮一個很窄的範圍,因為:1)它們的硬體結構僅滿足特定任務的操作;2)硬體和軟體之間的介面更簡單。具體來說,由於加速器在給定的域內執行,加速器程式的程式碼應該更緊湊,因為它編碼的資料更少。

舉個例子,假如你要開一家餐廳,但面積、用電預算是有限的。現在你要決定這個餐廳具體做哪些菜,是比薩、素食、漢堡、壽司全做(a)還是隻做披薩(b)?

如果選 a,你的餐廳確實能滿足很多口味不同的顧客,但你的廚師就要做很多菜,而且不見得每種都擅長。此外,你可能還需要買多個冰箱來儲存不同的食材,並密切關注哪些食材用完了,哪些變質了,不同的食材還有可能混在一起,管理成本大大提高。

但如果選 b,你就可以僱傭一位頂級的披薩專家,準備少量的配料,再買一臺定製的烤箱來做披薩。你的廚房會非常整潔、高效:一張桌子做麵糰,一張桌子放醬汁和乳酪,一張桌子放配料。但同時,這種做法也有風險:如果明天沒有人想吃披薩怎麼辦?如果大家想吃的披薩用你定製的烤箱做不出來怎麼辦?你已經花了很多錢打造這個專門化的廚房,現在是進退兩難:不改造廚房就可能面臨關店,改造又要花一大筆錢,而且改完之後,客戶的口味可能又變了。

回到處理器世界:類比上面的例子,CPU 就相當於選項 a,面向特定領域的加速器就是選項 b,店面大小限制就相當於矽預算。你將如何設計你的晶片?顯然,現實並沒有那麼兩極分化,而是有一個類似光譜的過渡區域。在這個光譜中,人們或多或少地用通用性來換取效率。早期的硬體加速器是為一些特定領域設計的,如數字訊號處理、網路處理,或者作為主 CPU 的輔助協處理器。

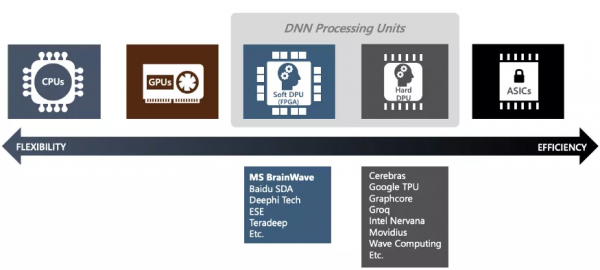

從 CPU 到主要加速應用領域的第一個轉變是 GPU。一個 CPU 有幾個複雜的處理核心,每個核心都採用各種技巧,比如分支預測器和亂序執行引擎,以儘可能加快單執行緒作業的速度。GPU 的結構則有所不同。GPU 由許多簡單的核心組成,這些核心具有簡單的控制流並執行簡單的程式。最初,GPU 用於圖形應用,如計算機遊戲,因為這些應用包含由數千或數百萬畫素組成的影象,每個畫素都可以並行獨立計算。一個 GPU 程式通常由一些核函式組成,稱為「核心(kernel)」。每個核心都包含一系列簡單的計算,並在不同的資料部分(如一個畫素或包含幾個畫素的 patch)執行數千次。這些屬性使得圖形應用成為硬體加速的目標。它們行為簡單,因此不需要分支預測器形式的複雜指令控制流;它們只需要少量操作,因此不需要複雜的算術單元(比如計算正弦函式或進行 64 位浮點除法的單元)。人們後來發現,這些屬性不僅適用於圖形應用,GPU 的適用性還可以擴充套件到其他領域,如線性代數或科學應用。如今,加速計算已經不僅僅侷限於 GPU。從完全可程式設計但低效的 CPU 到高效但可程式設計性有限的 ASIC,加速計算的概念無處不在。

深度神經網路的處理替代方案。來源:微軟。

如今,隨著越來越多表現出「良好」特性的應用程式成為加速的目標,加速器越來越受關注:影片編解碼器、資料庫處理器、加密貨幣礦機、分子動力學,當然還有人工智慧。

是什麼讓 AI 成為加速目標?

商業可行性

設計晶片是一個費力、耗資的事情——你需要聘請行業專家、使用昂貴的工具進行晶片設計和驗證、開發原型以及製造晶片。如果你想使用尖端的製程(例如現在的 5nm CMOS),耗資將達到數千萬美元,不論成功或失敗。幸運的是,對於人工智慧來說,花錢不是問題。AI 的潛在收益是巨大的,AI 平臺有望在不久的將來產生數萬億美元的收入。如果你的想法足夠好,你應該能夠很容易地為這項工作找到資金。

AI 是一個「可加速」的應用領域

AI 程式具有使其適用於硬體加速的所有屬性。首先最重要的是,它們是大規模並行的:大部分計算都花在張量運算上,如卷積或自注意力運算元。如果可能,還可以增加 batch size,以便硬體一次處理多個樣本,提高硬體利用率並進一步推動並行性。硬體處理器驅動其快速執行能力的主要因素是平行計算。其次,AI 計算僅限於少數運算種類:主要是線性代數核的乘法和加法、一些非線性運算元,例如模擬突觸啟用的 ReLU,以及基於 softmax 的分類的指數運算。狹窄的問題空間使我們能夠簡化計算硬體,專注於某些運算子。

最後,由於 AI 程式可以表示為計算圖,因此我們可以在編譯時知道控制流,就像具有已知迭代次數的 for 迴圈一樣,通訊和資料重用模式也相當受限,因此可以表徵我們需要哪些網路拓撲在不同計算單元和軟體定義的暫存儲存器之間通訊資料,以控制資料的儲存和編排方式。

AI 演算法是以硬體友好的方式構建的

不久之前,如果你想在計算架構領域進行創新,你可能會說:「我有一個新的架構改進的想法,它可以顯著地提高一些東西,但是——我需要做的就是稍微改變程式設計介面並讓程式設計師使用這個功能。」在那個時候這種想法會行不通。程式設計師的 API 是不可觸及的,而且用破壞程式「乾淨」語義流的低階細節來加重程式設計師的負擔是很難的。

此外,將底層架構細節與面向程式設計師的程式碼混合在一起並不是一個好習慣。首先它是不可移植的,因為某些架構特徵在晶片代際之間發生變化。其次它可能會被錯誤地程式設計,因為大多數程式設計師對底層硬體沒有深入的瞭解。

雖然你可以說 GPU 和多核 CPU 已經因為多執行緒(有時甚至是——記憶體牆)偏離了傳統的程式設計模型,但由於單執行緒效能早已不是指數級增長,我們只能將希望訴諸於多執行緒程式設計,因為這是我們唯一的選擇。多執行緒程式設計仍然很難掌握,需要大量的教育。幸運的是,當人們編寫 AI 程式時,他們會使用神經層和其他定義明確的塊來構建計算圖。

高階程式程式碼(例如 TensorFlow 或 PyTorch 中的程式碼)已經在以一種可以標記並行塊並構建資料流圖的方式編寫。因此理論上,你可以構建豐富的軟體庫和足夠精細的編譯器工具鏈來理解程式的語義並將其有效地降為硬體表示,而無需開發應用程式的程式設計師做任何參與,讓資料科學家做他們的事情,他們可以不在乎任務在哪些硬體上執行。在實踐中,編譯器完全成熟還需要時間。

幾乎沒有其他選擇

人工智慧無處不在,大型資料中心、智慧手機、感測器,機器人和自動駕駛汽車中都有它的身影。每個系統都有不同的現實限制:人們肯定不願意自動駕駛汽車因為算力太小而無法檢測障礙物,也不能接受因為效率低而在訓練超大規模預訓練模型時每天多花數千美元,AI 的硬體不存在一個晶片適用所有場景的說法,計算需求巨大,每一點效率都意味著花費大量的時間、精力和成本。如果沒有適當的加速硬體來滿足你的 AI 需求,對 AI 進行實驗和發現的能力將受到限制。

原文連結:

https://medium.com/@adi.fu7/ai-accelerators-part-ii-transistors-and-pizza-or-why-do-we-need-accelerators-75738642fdaa