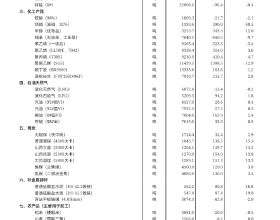

車載雷達是高階輔助駕駛(ADAS), 無人駕駛核心感測器之一,而車載雷達晶片是車載雷達的核心,如今高度整合(MMIC + DSP/MCU)的車規級晶片為雷達小型化,高可靠性與穩定性,低成本提供關鍵途徑,其重要性不言而喻。

近期,TI公司正式上線下一代車規級高效能車載雷達晶片,AWR2944,同時釋出與之配套的SDK,mmwave_mcuplus_sdk_04_02_00_01,參考設計工具箱toolbox, mmwave_automotive_toolbox_3_5_0,以及demo參考板 AWR2944 EVM,那麼這次釋出帶來哪些調整與升級,代表TI公司哪些雷達晶片產品設計思路,可能會對車載雷達行業產生哪些影響,我們來個deep dive。

AWR2944 TI定義為第二代車規級高效能車載雷達晶片,目前處於Preview階段。也就是可以提供晶片樣品或者可供評估的demo板,未正式規模量產。

▲ AWR2944

先來個關鍵點Device Overview

- AWR2944依舊是祖傳45nm RFCMOS工藝,支援76-81GHz頻段,最高5GHz頻寬。同時晶片支援4Tx4Rx,這也是TI迄今為止單晶片收發天線數目最多的晶片;

- 相位噪聲控制較之前的AWR1xxx系列略有提升,達到 -96 dBc/Hz [76 to 77 GHz]以及-95 dBc/Hz [76 to 81 GHz](Phase Noise @ 1MHz);

- 全新發射端移相器;

- DSS整合自家DSP,只不過型號由之前的C674x,調整為C66x。MSS中的處理器由ARM R4F升級為ARM R5F,硬體加速器(HWA)升級為2.0;

- 片上RAM提升至4MB;

- 首次整合硬體安全模組(Hardware Security Module,HSM),HSM本身主要由一個可程式設計的ARM Cortex M4核構成,此外,還對boot加入認證及加密機制(Secure authenticated and encrypted boot support)以及支援加密HWA,進一步加強雷達硬體安全;

- 車載通訊介面方面,2路CAN全部調整為CAN-FD,並首次支援百兆乙太網(10/100 Mbps RGMII/RMII/MII Ethernet);

- ADC取樣率37.5Msps,通道數提升至9路,UART提升至4路,新增CSI2 Rx interface用於採集資料回放;

- 接收端TI拋棄了上一代普遍採用的I/Q正交混頻結構,採用I路混頻結構(如下圖)

▲ Receive Subsystem (Per Channel)

硬體架構如下圖,AWR2944依舊是清晰的模組設計,前面介紹的各種調整與升級基本一目瞭然。我也放了AWR1843 的框圖,大家方便對比。

▲ Functional Block Diagram(AWR2944)

▲ Functional Block Diagram(AWR1843)

由此可見,作為第二代高效能雷達晶片,AWR2944調整升級的地方確實還蠻多。但是引數功能終究只是表面,我們還得看看這些調整升級背後的深層次邏輯。

我在“下一代角雷達-從SRR600說起”介紹過Conti下一代角雷達樣態,在大FoV條件下實現遠距離目標高精度感知是基本要求,這對雷達測距效能,角度FoV,解析度及精度提出新挑戰。

2944較前代又多整合一路傳送通道,以實現更高角度解析度及精度,同時也為更多複雜天線佈局設計提供晶片層面支援。

通常遠距離感知主要由天線設計解決,相對聚焦的波束測得更遠,同時壓縮了FoV,在大FoV條件下實現遠距離測距是比較困難的,一種途徑就是多天線同時傳送,比如4路天線同時發射,疊加的寬波束能夠在保證寬FoV條件下,距離測得更遠。但同發的問題在於接收端對疊加的波束可靠分離較為困難。2944採用了全新的DDM-MIMO通道分離方案(下文會詳述),在同發的基礎上實現可靠的通道分離,基本實現大FoV條件下遠距離目標高精度感知。並且這一切幾乎全由硬體加速器實現(只有部分少量計算由DSP介入),因此TI 將HWA順勢升級為2.0。

同時提高RAM容量以平衡通道數提升以及演算法複雜度提升帶來的記憶體開銷增大。乙太網介面的加入也是應對雷達輸出點雲等資料量提升問題。

1代晶片中,打頭陣的是1642,DSP是絕對的計算核心,用於幾乎全部的訊號處理及資料處理任務。MCU基本只用於配置,控制及管理等,這是TI對ARM MCU的基本定位。所以MSS及DSS的處理方式並不平衡,用TI的原話就是

In most use cases the MSS is defined as a control domain while the DSS actually executes the DPC.

*/ti/mmwave_mcuplus_sdk_04_02_00_01/mmwave_mcuplus_sdk_04_02_00_01/ti/control/dpm/docs/doxygen/html/index.html

而到了第2代,打頭陣的2944中,DSP地位被相當弱化,耗時耗力的訊號處理部分基本由HWA代勞,事實上,只要你願意,整個RSP處理鏈路皆由HWA實現,TI也希望你多多使用HWA,也因此調低了DSP規格,C66x處理頻率只有360MHz,遠低於上代C67x的600MHz。並且ARM也被加強,不僅用於配置及控制,也用於上層資料處理,比如tracking,classification也可由ARM處理,進一步分擔了DSP的處理任務,這是DSP規格下降的理由。

這樣的變化喜憂參半,文末再敘。

雖然2944調整升級豐富,帶來全新雷達體驗,但由於DSP規格降低,以及接收端單路混頻方案ADC數量降低等因素, 2944晶片成本不會提高很多。

軟體及demo參考設計方面

TI提供了適配2944的SDK及Toolbox。

Toolbox中包含滿足NCAP R79功能需求的2944參考設計,支援BSD, FCTA,LCA等。demo實現水平FoV ±80°下200m測距,角度解析度9.5°。比較有意思的是,TI在reference design 的feature欄中加入了這麼一句值得玩味的話:Builds customer confidence on mmWave device capabilities,看來毫米波雷達還是比較卑微啊。

▲ AWR2944 EVM

EVM與DCA1000結合提供raw data採集能力,為分析原始ADC資料提供支援。

Demo板天線MIMO佈局等效陣為

▲ Virtual Antenna Array

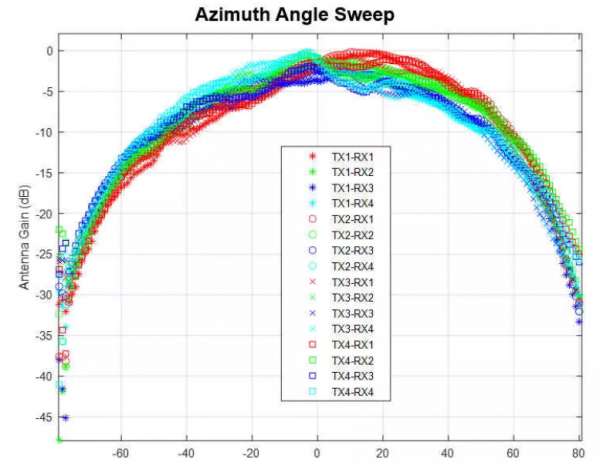

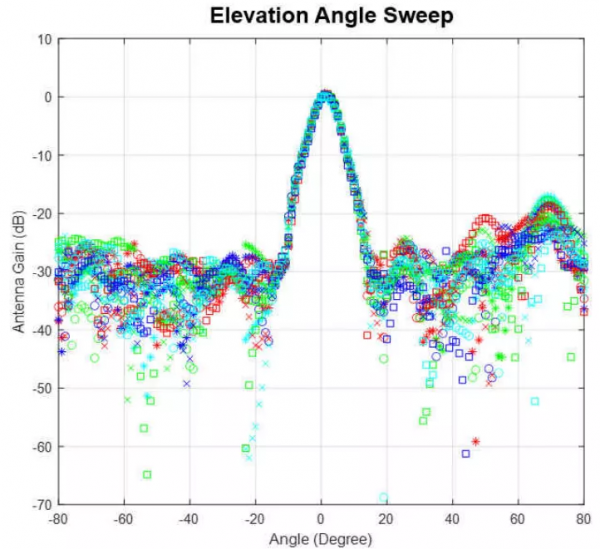

天線頻段覆蓋76GHz至81GHz,增益13dBi, 3dB波束寬度水平±30°,俯仰±3°。6dB波束寬度水平±45°,俯仰±5°。

▲ Azimuth Radiation Pattern

▲ Elevation Radiation Pattern

TI在SDK 3.x之後設計了全新的SW Framework,引入DPC,DPM,DPU等概念,使得整個軟體架構雖複雜但邏輯較為清晰,開發者能夠快速上手開發。Framework不是本文重點,不再贅述,聊聊核心升級DDM-MIMO。

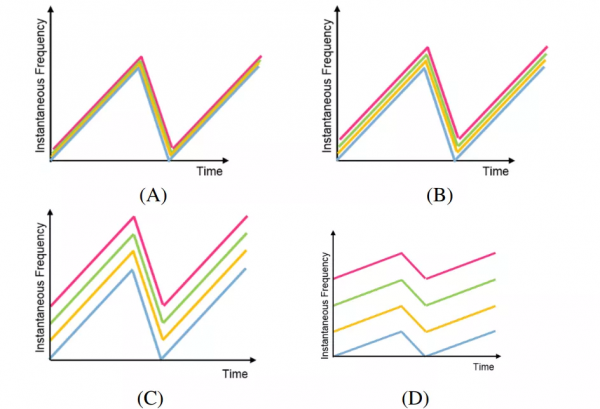

我在“4D雷達之MIMO通道”分離中討論過,FDM,TDM,CDM等MIMO通道分離技術。與TDMA不同,FDMA可以實現同發,並利用發射端天線與頻率偏移位置之間的對映關係確定通道分離方案。

其中FDM可以由下圖簡單總結:

(A) 如果各待分離通道之間的頻率偏移量是多普勒解析度的倍數,則是DDMA;

(B) 如果各待分離通道之間的頻率偏移量是dechirp後訊號頻寬的倍數,則是RDMA;

(C) 如果各待分離通道之間的頻率偏移量是最大拍頻的倍數,則是BFD;

(D) 如果各待分離通道之間的頻率偏移量是chirp頻寬的倍數,則是FT-FDMA。

▲ MIMO channel separation

由此可見,DDM可以認為是FDM的一種情況。

▲ range-Doppler map(DDM)

TI實現的是 The empty-band DDMA,提供RangeProc DDMA DPU,以及Doppler DDMA DPU構成DDMA核心實現模組。我簡單看了下TI 目前硬體實現的DDMA Demodulation,整體完成度還是可以的。

▲ DDMA principle

從DDMA modulation可見,DDM-MIMO對移相器要求很高,TI的移相器精度也需要仔細評估。

▲ Object Detection Data Path Processing Chain

不過DDMA也不是高枕無憂的方案,DDMA潛在問題包括但不限於,

- 相位校準

- 峰值混疊

- 不均衡幅值

下圖為demo實測效果,其測距效能,點雲密度,FoV等方面效果還可以,比1代確實有較大提升。希望能夠“Builds customer confidence on mmWave device capabilities”。

▲ 2944demo Test

小結

我們再上升一個臺階,分析TI 2944的釋出可能會對車載雷達行業產生哪些影響。

若僅從技術角度分析雷達競爭力,最重要在於天線,MMIC,演算法。晶片廠商提供MMIC,雷達廠商因天線及演算法上的優勢逐漸建立自身壁壘,而這一狀態似乎慢慢發生變化。

1、 毫米波雷達正逐漸從“訊號處理環節差異性”轉向“資料處理環節差異性”,也即是對點雲資料處理方式的差異性。TI倡導HWA的使用,將諸多先進訊號處理演算法固化,使用者只需按需取用,訊號處理演算法正在被標準化,構建雷達底層標準品。

降低DSP的處理頻率,提高ARM核心主頻,一方面變相引導使用者強化對HWA的使用,另一方面也有利於均衡成本。TI也表示:

The Hardware Accelerator block (HWA 2.0) supplements the DSS and MSS by offloading common radar processing such as FFT, Constant False Alarm rate (CFAR), scaling, and compression. This saves MIPS on the DSS and MSS, opening up resources for custom applications and higher level algorithms.

https://www.ti.com/lit/ds/symlink/awr2944.pdf?ts=1637431154585

雷達廠商的戰場慢慢向資料處理,包括跟蹤,目標分類,場景理解,邊緣AI,資料融合等環節。

2、我始終認為訊號處理才是毫米波雷達最迷人的地方。這樣的舉措無疑導致,雷達廠商從ADC原始資料輸出到雷達點雲資料輸出的所有中間環節掌控將越來越弱。降低RSP層靈活性。也會進一步降低了雷達技術門檻,打破原有雷達廠商部分技術壁壘。由此可見,晶片供應商對雷達廠商的影響會越來越大,晶片廠商頂層的“平權”策略進一步降低雷達廠商之間產品差異性,勢必進入低價競爭。

至於後續雷達的升級方向,我覺得訊號處理部分會在晶片廠商的影響下部分淡化,由HWA依舊會加強,RSP部分最終可能就是標準品,你需要怎麼樣的應用,配置下暫存器就好了,競爭可能越來越集中在上層資料處理,整合全新的AI Engine也是很有可能的,某種程度上,毫米波雷達除了頻段,會越來越像鐳射雷達。