摘要:

特斯拉的全自動駕駛 (FSD) 系統是世界上第一臺專用自動駕駛的高要求工作負載的計算系統。它基於一個新系統將 CPU、ISP 和 GPU 等行業標準組件整合在一起的晶片 (SoC),使用特斯拉的定製神經網路加速器。

FSD 計算機能夠處理高達每秒 2300 幀,位元斯拉之前的硬體提升了 21 倍,而且成本更低,最重要的是,它的效能在得到充分利用時,可在道路上實現更高水平的安全性和自主性。

特斯拉全自動駕駛(FSD)平臺和晶片目標

特斯拉全自動駕駛的主要目標是將(FSD) 計算機打造成一個用於當前和未來的資料處理的硬體平臺與全自動駕駛相關的需求。

此外,特斯拉的(FSD)系統在2016年10月份以來生產的任何特斯拉汽車中都引入了形式上的主要限制因數和熱包絡線,以適應冷卻能力有限的舊車。

FSD計算機的核心是世界上第一個專為自動駕駛的晶片。我們為神經網路推理提供了72個TOP的硬體加速器,批處理大小為1的初始工作負載的利用率超過80%。我們還包括一組用於控制需要的CPU、ISP、GPU和用於各種預處理的影片編碼器以及後處理需求。所有這些都緊密整合,以滿足每個晶片低於40瓦的極具攻擊性的TDP。

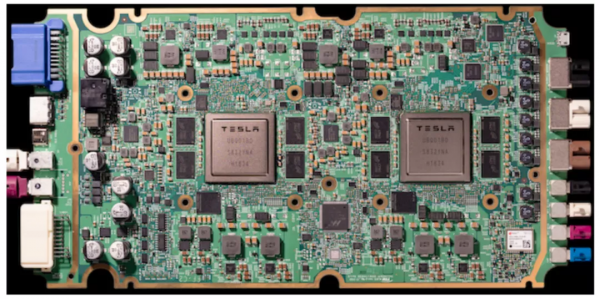

圖1。FSD計算機,具有兩個特斯拉FSD晶片,採用雙配置,包括攝像頭等感測器。

該系統包括兩個獨立啟動並執行獨立作業系統的FSD晶片例項。這兩種情況還允許獨立的電源和感測器,以確保系統的異常安全水平。如圖1所示的計算機滿足與舊硬體的形式、配合和介面級相容性。

FSD晶片

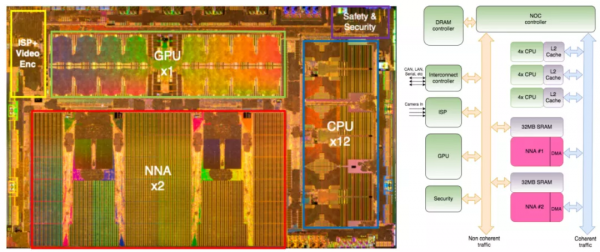

FSD晶片是一個260平方毫米的晶片,擁有約2.5億個柵極或60億個電晶體,由三星採用14奈米FinFet技術製造。如圖2所示,晶片封裝在37.5毫米 37.5毫米倒裝晶片BGA封裝中。該晶片符合AEC-Q100 2級可靠性標準

圖2(a)顯示了晶片中的主要模組。我們從頭開始設計了兩個神經網路加速器(NNA)例項,併為系統的其餘部分選擇了行業標準IP,如A72 CPU、G71 GPU和ISP。休息晶片的未標記區域由外圍裝置組成,NOC結構和記憶體介面。每個NNA有32-MBSRAM和96*96 MAC陣列。在2GHz時,每個NNA提供36個頂部,FSD晶片總計72個頂部。

FSD SoC,如圖所示在圖2(b)中,提供了通用CPU執行大多數自動駕駛儀演算法。

每隔幾毫秒,新的輸入幀透過dedi定位的影象訊號處理器接收,在儲存到DRAM之前進行預處理。一旦主記憶體中有了新的幀,CPU就會指示NNA加速器開始處理它們。加速器控制資料和引數流到它們的本地SRAM,以及流回的結果直截了當地說。一旦得到相應的結果幀已經發送到DRAM,加速器觸發一箇中斷返回到CPU複合體。GPU可用於任何後處理可能需要NNA加速器不支援的演算法的任務。

圖2。(a) 主要模組的FSD晶片模具照片。(b) SoC框圖。

晶片設計方法

我們的設計方法是為滿足積極的開發時間表而定製的。為此,我們決定構建一個定製加速器,因為它提供了比上一代產品更高的效能和功耗。我們使用了可用的硬IP或軟IP該技術節點用於剩餘的SoC塊,以減少開發進度風險。

我們混合使用了行業標準工具和用於廣泛應用的開源工具,如verilator模擬我們的設計。Verilator模擬特別適合長時間的測試(例如執行整個神經網路),其中他們放棄了比商業模擬器高出50的加速比。另一方面,verilator下的設計比較緩慢,因此我們依賴用於快速週轉的商用模擬器並在RTL開發階段進行除錯。除了模擬,我們還廣泛使用硬體模擬器,以確保高度的SoC的功能驗證。

對於加速器的定時關閉,我們設定了一個非常積極的目標,大約比最終裝運頻率2 GHz高25%。這使得設計執行遠低於Vmax,在我們的功率預算內提供最高的效能,正如矽表徵後測量的那樣。

神經網路加速器設計動機

神經網路加速器

設計動機

自定義NNA用於檢測預先定義的一組物件,包括但不限於車道線、行人、不同型別的車輛,幀速率非常高,功率預算適中,如平臺目標所述。

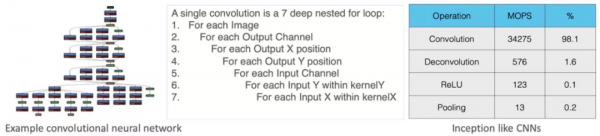

圖3。初始網路、卷積迴圈和執行配置檔案

圖3顯示了一個典型的初始卷積神經網路。1,2網路有許多層和連線,指示通訊資料流或啟用。每個透過這個網路的過程都涉及到一個影象,以及在每一層之後依次構建的各種功能或啟用。在最後一層之後檢測到物件。

如圖3所示,98%以上的操作屬於卷積。卷積演算法由七個深巢狀迴圈組成,如圖3所示。最內層迴圈中的計算是一種乘法累加(MAC)操作。因此,我們設計的主要目標是儘可能快地執行大量MAC操作,同時不增加功率預算。

按數量級加快卷積將導致量化或池化等操作的頻率降低,如果這些操作的效能顯著降低,則它們將成為整體效能的瓶頸。這些行動還使用專用硬體進行了最佳化,以提高整體效能。

卷積重構與資料流

圖4。卷積重構和資料流。

卷積迴圈,經過一些重構,如圖4(a)所示。仔細檢查表明這是一個令人尷尬的平行有很多機會處理問題並行的MAC操作。在卷積中迴圈中MAC操作的執行三個最裡面的迴圈,它們決定了每個點積的長度在很大程度上是連續的。但是,在三個外部迴圈,即對於每個影象,對於每個輸出通道,用於每個輸出中的所有畫素通道,是可並行的。但這仍然是一個艱難的過程由於記憶體頻寬過大而導致的問題需求和功率的顯著增加消費支援如此之大的平行計算因此,在本文的其餘部分,我們將主要關注這兩個方面。

首先要注意的是,並行處理多個影象對我們來說是不可行的。出於安全考慮,我們不能等待所有影象到達後啟動計算,因為這會增加目標檢測的延遲。我們需要在影象到達後立即開始處理它們。相反,我們將跨多個輸出通道和每個輸出通道內的多個輸出畫素平行計算。

圖4(a)顯示了重構卷積迴圈,優化了資料重用以降低功耗並提高實現的計算頻寬。我們合併每個輸出通道的兩個維度,並以行主形式將它們展平為一維,如步驟(2)、圖4(a)所示。這提供了許多並行的輸出畫素,而不會丟失所需輸入資料的區域性連續性。

我們還將迴圈切換為迭代每個輸出通道內的畫素,如圖4(a)的步驟(2)和(3)所示。對於一組固定的輸出畫素,我們首先在輸出通道的子集上迭代,然後再移動到下一組輸出畫素以進行下一次傳遞。一個這樣的過程,將輸出通道子集內的一組輸出畫素組合起來,可以作為平行計算形成。我們繼續這個過程,直到在輸出通道的第一個子集中耗盡所有畫素。一旦所有畫素耗盡,我們將移動到下一個輸出通道子集並重復該過程。這使我們能夠最大限度地實現資料共享,就像所有輸出通道內相同畫素集的計算使用相同的輸入資料。

圖4(b)–(d)也說明了資料流透過上面的卷積重構層連續影象的相同輸出畫素輸出通道透過共享輸入啟用和連續輸出畫素在同一輸出通道內計算透過共享輸入權重。這種分享點積計算的資料和權重有助於利用大型計算頻寬,同時透過最小化移動資料的負載數量來降低功耗圍繞。

計算方案

圖5。計算方案。

最後一節中描述的重構卷積演算法適用於具有資料流的計算方案,如圖5所示。一個縮小的版本的物理96×96 MAC陣列顯示在中間為簡潔的空間,其中每個單元由一個單位實現MAC操作與一個單週期反饋迴路。頂部和左側的矩形網格是虛擬的,表示資料流。頂部網格(此處稱為資料網格)顯示了96個數據元素的縮小版本在每行中,左側網格(此處稱為權重網格)顯示每列中96個權重的縮小版本。資料網格和權重網格的高度和寬度等於點積的長度。

計算過程如下:資料網格的第一行和權重網格的第一列分別以流水線方式在幾個週期內跨MAC陣列的所有96行和96列廣播。每個小區使用廣播資料和本地權重計算MAC操作。在下一個週期中,以流水線方式廣播資料網格的第二行和權重網格的第二列,並且類似地執行每個小區中的MAC計算。此計算過程將繼續,直到資料和權重網格的所有行和列都已廣播,並且所有MAC操作都已完成。因此,與許多其他處理器中實現的脈動陣列計算不同,每個MAC單元在MAC陣列中本地計算點積而不移動資料。3,4這導致比脈動陣列實現更低的功率和更少的單元面積。

當所有MAC操作完成時,累加器值準備向下推送到SIMD單元進行後處理。這將建立第一個96輸出片,如圖5所示。後處理通常涉及量化操作,在96寬SIMD單元中執行。96寬SIMD單元的頻寬與每個輸出通道相關的96元素累加器輸出相匹配。MAC陣列中的累加器行以每週期一行的速率下移到SIMD單元。從物理上講,累加器行每八個週期僅移動一次,一組八個。這大大降低了移動累加器資料所消耗的功率。MAC引擎的另一個重要特性是MAC和SIMD操作的重疊。當累加器值被下推到SIMD單元進行後處理時,在MAC陣列中立即開始下一次卷積運算。這種重疊計算提高了計算頻寬的總體利用率,避免了死迴圈。

設計原則和指令集

建築學

上一節描述了計算的資料流。對於控制流,我們關注簡單性和電源效率。在現代無序CPU和GPGPU 5–7上執行的平均應用程式會消耗計算單元之外的大部分能量來移動指令和資料,並消耗昂貴的結構(如快取、暫存器檔案和分支預測器)。8此外,此類控制結構還引入了顯著的設計複雜性。我們的目標是設計一臺計算機,在這種計算機中,幾乎所有揮霍的控制結構都被消除,工作負載的執行將所有精力都花在對效能最重要的事情上,即MAC引擎上。為此,我們實現了一個非常靈活但非常熟練的狀態機,其中所有昂貴的控制流都內建到狀態機中,例如迴圈構造和融合。

另一個非常重要的效能和功耗最佳化功能是在卷積流期間消除DRAM讀寫。對於推斷,每個層的輸出資料由相關層使用,並且可以被覆蓋。載入初始啟用資料集後,該機器完全透過嵌入計算引擎本身的SRAM進行操作。

本設計理念在最後一節中概述。對於具有粗粒度可程式設計性的柔性狀態機,我們權衡了需要昂貴控制結構的細粒度可程式設計性。狀態機驅動的控制機制有助於形成一個非常緊湊但強大且靈活的ISA。只有七條主指令,以及各種附加控制欄位,用於設定狀態機以執行不同的任務:資料進出SRAM(DMA讀取和DMA寫入)、點積(卷積、反捲積、內積)和純SIMD(縮放、ELTWISE)。

資料移動指令的長度為32位元組,對源地址和目標地址、長度和依賴標誌進行編碼。計算指令長256位元組,對輸入地址進行編碼,最多可編碼三個張量(輸入啟用和權重或兩個啟用張量、輸出結果)、張量形狀和依賴標誌。它們還對各種引數進行編碼,這些引數描述了計算的性質(填充、跨步、擴充套件、資料型別等)、處理順序(行優先或列優先)、最佳化提示(輸入和輸出張量填充、預計算狀態機欄位)、融合操作(縮放、偏移、池)。所有計算指令後面都可以跟有數量可變的SIMD指令,這些指令描述了在所有點積輸出上執行的SIMD程式。因此,點積層(卷積、反捲積)可以透過簡單的運算(量化、縮放、ReLU)或更復雜的數學函式(如Sigmoid、Tanh等)進行融合。

網路程式

加速器可以同時執行DMA和計算指令。在每種型別中,指令都是按順序執行的,但可以在它們之間重新排序以實現併發性。生產者/消費者排序使用顯式依賴標誌進行維護。

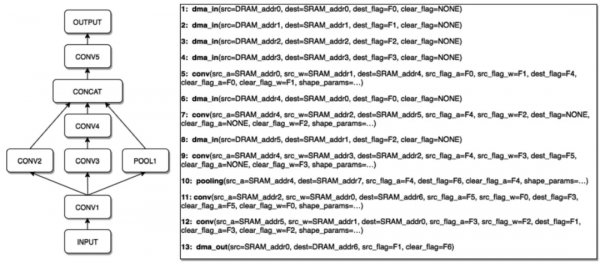

圖6。典型網路程式

典型程式如圖6所示。該程式從幾個DMA讀取操作開始,將資料和權重帶入加速器的SRAM。解析器將它們插入佇列,並在第一條計算指令處停止。一旦掛起的計算指令的資料和權重在SRAM中可用,就會設定它們相應的依賴標誌,並且計算指令可以開始與其他排隊的DMA操作並行執行。

依賴標誌用於跟蹤資料可用性和緩衝區使用情況。如圖6所示,在步驟6中執行的DMA覆蓋了由前面的卷積(步驟5)產生的一個緩衝區。因此,在卷積結束時清除其目標標誌(F0)之前,它不能開始執行。然而,使用不同的目標緩衝區和標誌將允許執行中的DMA與前面的卷積並行執行

我們的編譯器採用Caffe格式的高階網路表示,並將其轉換為類似於圖6中的指令序列。它分析計算圖,並根據資料流、融合或分割槽層對其進行排序,以匹配硬體功能。它為中間結果和權重張量分配SRAM空間,並透過依賴標誌管理執行順序

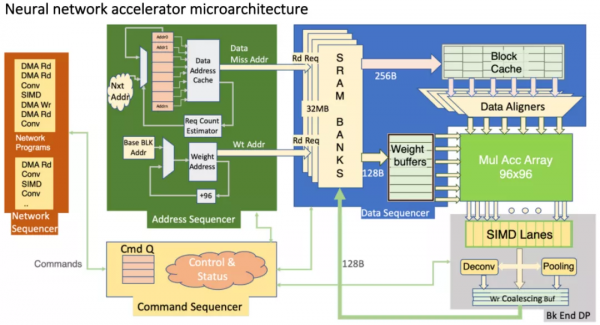

NNA微體系結構

圖7。NNA微體系結構。

如圖7所示,NNA圍繞兩個主要資料路徑(dot product engine和SIMD unit)和狀態機進行組織,狀態機解釋程式、生成記憶體請求流,並控制資料路徑內外的資料移動。

點積引擎

如“計算方案”部分所述,點積引擎是一個96個MAC單元陣列。每個單元接受兩個8位整數輸入(有符號或無符號),並將它們相乘,將結果新增到30位寬的本地累加器暫存器中。有許多處理器使用單精度或半精度浮點(FP)資料和推理權重部署浮點運算。我們的integer MAC compute具有足夠的範圍和精度,能夠以所需的精度執行所有特斯拉工作負載,並且與使用FP演算法的計算相比,其功耗低一個數量級。

在每個週期中,陣列接收兩個向量,每個向量96個元素,並將第一個向量的每個元素與第二個向量的每個元素相乘。結果將就地累積,直到dot產品序列結束,然後解除安裝到SIMD引擎進行進一步處理

每個累加器單元圍繞兩個30位暫存器構建:累加器和移位暫存器。一旦計算序列完成,點積結果被複制到移位暫存器中,累加器被清除。這允許結果透過SIMD引擎移出,而下一個計算階段在點積引擎中開始

單指令多資料單元

SIMD單元是一個96寬的資料路徑,可以執行全套算術指令。它從點積引擎(一個累加器行)一次讀取96個值,並作為指令序列(SIMD程式)執行後處理操作。SIMD程式無法直接訪問SRAM,且不支援流量控制指令(分支)。對從MAC陣列解除安裝的每組96個值執行相同的程式。

SIMD單元可透過具有各種資料型別、8位、16位和32位整數以及單精度浮點(FP32)的豐富指令集進行程式設計。指令集還為控制流提供條件執行。輸入資料始終為30位寬(強制轉換為int32),最終輸出始終為8位寬(有符號或無符號int8),但中間資料格式可能不同於輸入或輸出

由於大多數常見的SIMD程式都可以用一條稱為FusedReLu(FusedQuantization,scale,ReLU)的指令來表示,因此指令格式允許將任何算術運算與移位和輸出運算相融合。FuseDelu指令是完全流水線的,允許96點產品引擎在96個週期內解除安裝。更復雜的後處理序列需要額外的指令,從而增加了點積引擎的解除安裝時間。一些複雜序列是由FP32指令和條件執行構建的。30位累加器值在此類SIMD程式開始時轉換為FP32運算元,FP32結果在SIMD程式結束時轉換回8位整數輸出

聯合支援

在SIMD單元中進行後處理後,輸出資料也可以有條件地透過池單元進行路由。這允許最頻繁的小型核心池操作(2和3)在SIMD執行的陰影下執行,與生成資料的早期層並行。池硬體實現對齊器,將重新排列以最佳化卷積的輸出畫素對齊回原始格式。池單元有三個96位元組96位元組池陣列,具有位元組級控制。較不頻繁的較大核心池操作在dotproduct引擎中作為卷積層執行。

記憶組織

NNA使用32-MB本地SRAM儲存權重和啟用。為了同時實現高頻寬和高密度,SRAM使用許多相對較慢的單埠組來實現。每個週期可以訪問多個這樣的儲存組,但為了保持較高的單元密度,不能在連續週期中訪問儲存組

SRAM透過兩個獨立的讀取埠(256位元組和128位元組寬)每個週期可提供多達384位元組的資料。仲裁器對來自多個來源(權重、啟用、程式指令、DMA輸出等)的請求進行優先順序排序,並透過兩個埠對它們進行排序。來自同一來源的請求不能被重新排序,但是來自不同來源的請求可以被優先排序以最小化銀行衝突

在推理過程中,權重張量始終是靜態的,可以在SRAM中佈局,以確保有效的讀取模式。對於啟用,這並不總是可能的,因此加速器將最近讀取的資料儲存在1-kB的快取中。這有助於透過消除相同資料的背對背讀取來最小化SRAM組衝突。為了進一步減少銀行衝突,加速器可以使用網路程式提示的不同模式填充輸入和/或輸出資料。

控制邏輯

如圖7所示,控制邏輯分為幾個不同的狀態機:命令序列器、網路序列器、地址和資料序列器以及SIMD單元

每個NNA可以將多個網路程式排隊並按順序執行。命令序列器維護此類程式的佇列及其相應的狀態暫存器。一旦網路執行完成,加速器就會觸發主機系統中的中斷。在其中一個CPU上執行的軟體可以檢查完成狀態,並重新啟用網路以處理新的輸入幀。

網路定序器解釋程式指令。如前所述,指令是長資料包,編碼足夠的資訊以初始化執行狀態機。Network Sequencer對該資訊進行解碼並將其引導到適當的使用者,強制執行依賴項並同步機器,以避免生產者和使用者層之間的潛在競爭條件。

一旦一條計算指令被解碼並引導到其執行狀態機,地址序列器就會為下游的計算生成SRAM地址和命令流。它將輸出空間劃分為最多96個元素的部分,並且對於每個這樣的部分,它將透過相應點積的所有項進行排序。

權重資料包在SRAM中預先排序以匹配執行,因此狀態機只需將它們以96個連續位元組的組進行流式處理。然而,啟用並不總是來自連續的地址,它們通常必須從多達96個不同的SRAM位置收集。在這種情況下,地址序列器必須為每個資料包生成多個載入地址。為了簡化實現並允許高時鐘頻率,96個元素的資料包被劃分為12個片段,每個片段8個元素。每個片由單個載入操作提供服務,因此其第一個和最後一個元素之間的最大距離必須小於256位元組。因此,透過發出1到12次獨立的載入操作,可以形成96次啟用的資料包。

負載資料與控制資訊一起轉發到資料定序器。權重在預取緩衝區中捕獲,並根據需要傳送給執行。啟用儲存在資料快取中,從中收集96個元素併發送到MAC陣列。資料路徑的命令也從資料序列器中匯入,控制執行啟用、累加器移位、SIMD程式啟動、儲存地址等。

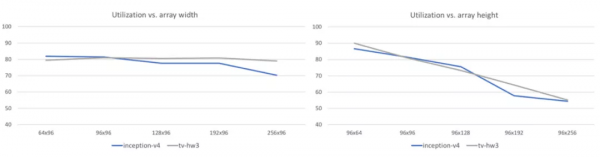

圖8。實現的利用率與MAC陣列維度

SIMD處理器對從MAC陣列解除安裝的每組96個累加器結果執行相同的程式。它由地址序列器內生成的控制資訊進行同步,它可以解碼、發出和執行SIMD算術指令流。雖然SIMD單元有自己的暫存器檔案,並控制資料路徑中的資料移動,但它不控制儲存結果的目標地址。當地址序列器選擇要處理的96 96輸出片時,它會生成儲存地址和任何池控制。

架構決策和結果

在實現我們的MAC陣列和SIMD處理器等非常廣泛的機器時,主要關注點總是與其工作時鐘頻率有關。高時鐘頻率使實現目標效能更容易,但它通常需要一些邏輯簡化,這反過來又會損害特定演算法的利用率。

我們決定對具有大量輸入和輸出通道的深卷積神經網路進行最佳化設計。SRAM每個週期向MAC陣列提供的192位元組的資料和權重只能完全用於跨距為1或2的層,而跨距較高的層往往利用率較低。

加速器的利用率可能會因MAC陣列的大小和形狀而顯著不同,如圖8所示。inception-v4和特斯拉視覺網路都對MAC陣列的高度非常敏感。雖然同時處理更多的輸出通道可能會影響總體利用率,但由於它們共享相同的輸入資料,因此這種能力相對便宜。增加陣列的寬度不會對利用率造成太大的影響,但它需要大量的硬體資源。在我們選擇的設計點(96 MAC陣列),這些網路的平均利用率略高於80%。

我們必須評估的另一個權衡是SRAM的大小。神經網路的規模越來越大,所以儘可能多地新增SRAM可能是一種未來驗證設計的方法。然而,更大的SRAM將增加晶片的流水線深度和總面積,從而增加功耗和系統的總成本。另一方面,一個太大而無法裝入SRAM的卷積層總是會被分解成多個較小的元件,這可能會為向DRAM溢位和填充資料付出一些代價。根據我們當前網路的需求和中期擴充套件預測,我們選擇了每個加速器32 MB的SRAM。

結論

特斯拉的FSD計算機比我們以前的硬體中使用的商用解決方案提供了卓越的21效能提升,同時降低了成本,所有這些都需要適度的25%額外功率。這一水平的效能是透過毫不妥協地堅持我們最初的設計原則實現的。在每一步中,我們都透過高度的資料重用和對控制流的最低限度設計來最大限度地利用可用的計算頻寬。該FSD計算機將是推進FSD特徵集的基礎。

從這項工作中學到的關鍵是效率和靈活性之間的權衡。具有固定功能硬體的定製解決方案提供最高的效率,而完全可程式設計的解決方案更靈活,但效率明顯較低。我們最終確定了一個解決方案,該解決方案具有可配置的fixedfunction硬體,可以非常高效地執行最常見的功能,但增加了一個可程式設計SIMD單元,它以較低的效率執行不太常見的功能。我們對特斯拉用於推理的工作量的瞭解使我們能夠以高度的信心進行這樣的權衡。

特斯拉的FSD計算機比我們以前的硬體中使用的商用解決方案提供了卓越的21倍效能提升,同時降低了成本,所有這些都需要適度的25%額外功率。這一水平的效能是透過毫不妥協地堅持我們最初的設計原則實現的。

作者:陌世

來源:編譯自-Theme Article: Hot Chips