現在我們都說摩爾定律逐漸走到極限,作為一個經濟學定律,摩爾定律逐漸不具備成本經濟的效益。首先高階工藝節點已達到物理電晶體尺寸極限,再者隨著伺服器CPU和GPU裸片尺寸隨時間推移不斷增加,裸片Die尺寸不斷增長已接近極限。所以,業界開始考慮從不同維度出發,來延續摩爾定律。

IC設計發展轉向3D維度

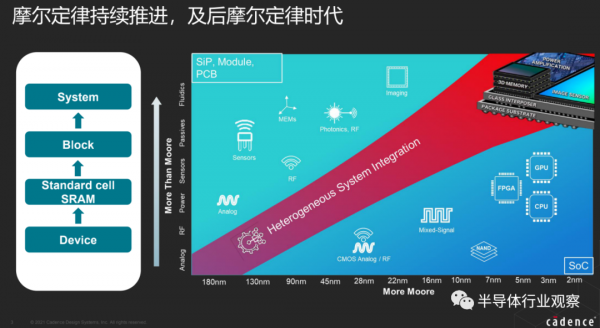

一個晶片的組成主要分為四個層次:最底層的器件,標準單元庫,片上記憶體SRAM,在SRAM上會做一個晶片的Block,再往上就是系統。為了讓摩爾定律繼續往下走,一方面的技術努力是More Moore,在這方面的探索主要有鋁介質,然後是銅,再就是High-K,FinFET,3奈米之後還有GAA,靠著這些技術摩爾定律在先進工藝上不斷向前發展。

但是光靠這一個維度是不足以支撐摩爾定律繼續往下走的,因為其成本看不到顯著的降低。所以業界還在探索另外一個維度,就是More than Moore,從系統角度出發,在封裝上下功夫,走堆疊的路線,如現在的2.5D封裝和3D封裝等。

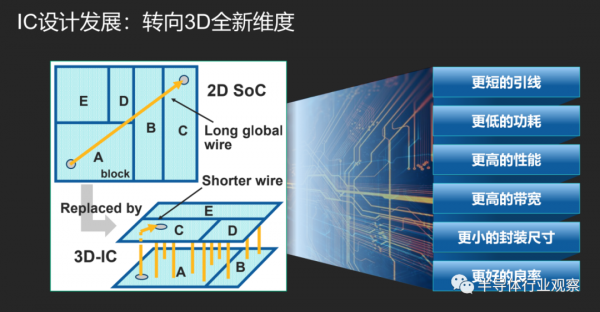

下圖是一張在顯微鏡下得到的封裝圖,在封裝裡面會有很大的焊球,這個焊球的大小影響了晶片的頻寬和速度。可以看出,如果一旦從2D走向3D的維度,其明顯的好處是焊球的連線變短了,連線變短之後,功耗也會更低,線上的Delay減少了以後,晶片就會跑的比以前更快,得到更好的效能。還有更加顯而易見的好處是,因為晶片被堆疊起來,其封裝的尺寸會小很多。最後就是更好的良率,要知道,在流片的過程中,良率和麵積是呈指數級關係的,面積越大,良率越低。

但是3D-IC設計當前還面臨著諸多挑戰,首先是聚合和管理上的挑戰,包括裸片的放置與Bump規劃,而且SoC和封裝團隊各自為戰,缺少代表多種技術的統一資料庫;再一個挑戰就是系統級驗證,需要有跨晶片/Chiplet及封裝的熱分析,還需要系統級的裸片間的連線驗證,3D STA籤核Corner也會有“爆炸性”的增加。而當前EDA行業的解決方案現狀是脫節,片面,點工具,無法進行探索/缺乏早期反饋,導致堆疊中單個裸片的過度設計,成本高昂。所有這一切都讓3D STA比2D複雜度高很多。

針對這些行業痛點和先進封裝技術發展趨勢,Cadence釋出了一款突破性的新產品。

Integrity 3D-IC 平臺:由系統驅動Chiplet PPA

要說明的是,在先進封裝領域,不止是封裝廠和晶圓廠們廠努力的方向,EDA軟體廠商也是先進封裝的重度探索者。例如,Cadence就已經在多個小晶片(Multi-Chiplet)封裝領域耕耘了20多年,從1980年開始做系統級的封裝,到2004年開始做RF模組,2010年開始研發2.5D技術,2012年開始做嵌入式的橋接,到現在,在比較流行的FOWLP、Bumpless 3D整合以及Co-package等,都是Cadence不斷髮力的方向,其中Co-package指的不僅是矽晶片,Cadence甚至可以把光和矽堆疊起來。

據Cadence數字與籤核事業部產品工程資深群總監劉淼的介紹,Cadence這些年正在努力轉型,以前我們只做EDA工具,後來我們做了更多系統級的創新,最後我們希望能達到普適的智慧,而3D-IC就是在系統創新上能夠做出來的幫助客戶解決當前痛點以及未來十年發展的趨勢。

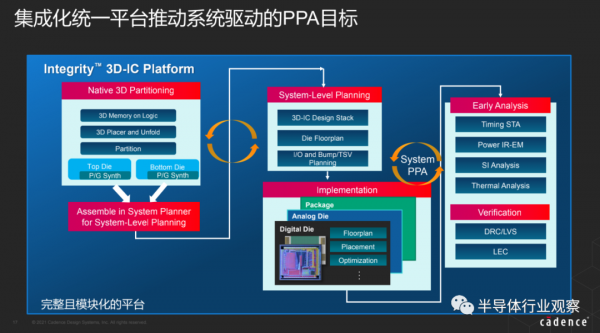

劉淼進一步指出,Cadence 3D-IC下一個十年從這幾個維度出發,第一是先進封裝的關鍵技術,在封裝領域有兩個趨勢,分別是模擬數字化和封裝晶圓化,Cadence將擁抱這些變化,發力先進封裝。再就是數字設計與籤核,我們提系統級的PPA,肯定跟數字設計要相容,所以我們要有統一的平臺。要做3D堆疊,只有數字就顯得沒有那麼全面,所以還要有模擬設計和驗證的加入。最後還要做熱模擬與訊號完整性分析。所有這一切都放在這個Integrity 3D-IC的平臺中。

Integrity 3D-IC平臺是業界首款完整的高容量 3D-IC 平臺,它將設計規劃、物理實現和系統分析統一集成於單個管理介面中。Integrity 3D-IC平臺支援了Cadence第三代 3D-IC 解決方案,客戶可以利用平臺整合的熱、功耗和靜態時序分析功能,最佳化受系統驅動的小晶片(Chilet)的功耗、效能和麵積目標(PPA)。

那麼Integrity 3D-IC平臺的“法寶”體現在哪些方面呢?讓我們娓娓道來。

萬物皆有源,Cadence的理解是,源就是要有一個統一的平臺,Cadence的Integrity平臺相容資料和模擬兩塊,能做到多層級、多技術、多層次、多模型的按需型資料庫,要做到這點實屬不易,這個相容性Cadence花了很多年才得以做出來。其實為了讓數字和模擬相容,早在20年前Cadence就推出開放資料庫,現在已經更近一步。有了統一的管理介面和資料庫,SoC和封裝設計團隊可以對完整系統進行完全同步的協同最佳化,更高效地將系統級反饋整合採納。

前面我們提到了一些關於3D IC設計的挑戰,3D設計比2D的設計還有一個挑戰是週期會長,針對這個問題,Cadence透過早期電熱及跨晶片STA,能夠在早期規避散熱和功耗的問題,以此來建立穩健的3D-IC設計,利用早期系統級反饋最佳化全系統PPA。

再一個就是時序的Signoff,3D的時序分析要比2D複雜的多,在這方面,Cadence有快速、自動裸片間分析技術(RAID),它可以顯著降低STA Corner資料和週轉週期。同時,Cadence還推出了另外一個並行多模式多Corner(C-MMMC)的技術,可以很好的簡化專案管理與機器資源。這兩個技術都是Cadence的強項。還可以透過裸片級分層能夠顯著降低邊界模型的資料量。最後是Tempus ECO選項,透過並行多裸片的3D-IC時序ECO,可以最佳化系統驅動PPA。

下圖就是交給客戶的流程,Integrity 3D-IC是一個完整且模組化的平臺,可以做Native 3D Partitioning,一開始系統級的工程師決定哪個在上哪個在下,做完以後可以做partition,可以在系統級裡做System -Level Planning。做完以後可以做die的floorplan等等。最終實現由系統來驅動的PPA目標。

Integrity 3D-IC在釋出的時候就得到了客戶的早期響應。imec也表示,得益於和Cadence的長期合作,我們成功找到了設計分割槽的自動化方法,以建立最優的3D堆疊,透過增加可用儲存器頻寬進一步提升先進工藝節點設計的效能,並降低功耗。根據我們研究團隊在多核高效能設計結果,Cadence Integrity 3D-IC平臺將儲存器整合在邏輯流程,實現了跨晶片(cross-die)設計規劃、設計實現和多Die的STA。

前文中我們有提到Cadence可以將光和矽片封裝在一起,在這方面,Cadence與Lightelligence有相關的合作。Lightelligence這些年一直在採用多晶片堆疊技術,意圖用光學計算技術推動AI的演進加速。而Integrity 3D-IC平臺正可以幫助Lightelligence使用光學計算技術加速AI設計,實現下一代創新。

“在3D領域中國還是很領先的”,劉淼坦言道,除了Lightelligence,中興微電子也是Cadence的合作物件,中興對3D堆疊尤其是通訊的3D堆疊很看重,通訊的功耗是一大要解決問題。Integrity 3D-IC平臺將最佳化的中階層設計實現和系統分析完美整合,提供快速、完整的系統分析,使中興微電子能夠提供滿足超大規模計算和 5G 通訊應用的記憶體頻寬需求的設計。

Integrity 3D-IC平臺的釋出,將對國內的多晶片3D堆疊技術大有裨益,它支援超大規模計算、消費電子、5G 通訊、移動和汽車等廣泛的應用場景。相較於傳統單一脫節的 Die-by-Die 設計實現方法,晶片設計工程師可以利用 Integrity 3D-IC 平臺獲得更高的生產效率。

*免責宣告:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅為了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支援,如果有任何異議,歡迎聯絡半導體行業觀察。

今天是《半導體行業觀察》為您分享的第2839內容,歡迎關注。

晶圓|積體電路|裝置|汽車晶片|儲存|臺積電|AI|封裝