文丨高工 汽車主機廠ADAS研發人員

先上部分概念:

CPU

CPU 中央處理器(Central Processing Unit)是一塊超大規模的積體電路,是一臺計算機的運算核心(Core)和控制核心( Control Unit)。它的功能主要是解釋計算機指令以及處理計算機軟體中的資料。中央處理器主要包括運算器(算術邏輯運算單元,ALU,Arithmetic Logic Unit)和高速緩衝儲存器(Cache)及實現它們之間聯絡的資料(Data)、控制及狀態的匯流排(Bus)。它與內部儲存器(Memory)和輸入/輸出(I/O)裝置合稱為電子計算機三大核心部件。

GPU

GPU 圖形處理器(Graphics Processing Unit),又稱顯示核心、視覺處理器、顯示晶片,是一種專門在個人電腦、工作站、遊戲機和一些移動裝置(如平板電腦、智慧手機等)上影象運算工作的微處理器。用途是將計算機系統所需要的顯示資訊進行轉換驅動,並向顯示器提供行掃描訊號,控制顯示器的正確顯示,是連線顯示器和個人電腦主機板的重要元件,也是“人機對話”的重要裝置之一。顯示卡作為電腦主機裡的一個重要組成部分,承擔輸出顯示圖形的任務,對於從事專業圖形設計的人來說,顯示卡非常重要。

NPU

NPU 嵌入式神經網路處理器,採用“資料驅動平行計算”的架構,特別擅長處理影片、影象類的海量多媒體資料。嵌入式NPU的小型化、低功耗和低成本優勢,加快人工智慧技術落地應用。例如無人機對攝像頭的重量和功耗有很高的要求,否則會影響起飛和續航能力。而“星光智慧一號”只有普通郵票大小,重量僅幾十克,它的誕生讓諸多監控攝像頭等小型裝置有了人工智慧化的可能,邁出了人工智慧從神秘的機房,跨向生活應用的一步。

TPU

TPU(Tensor Processing Unit),是谷歌打造的處理器,是專為機器學習量身定做的,執行每個操作所需的電晶體數量更少,自然效率更高。因為它能加速其第二代人工智慧系統TensorFlow的執行,而且效率也大大超過GPU——Google的深層神經網路就是由TensorFlow引擎驅動的。

MPU

MPU有兩種意思,微處理器和記憶體保護單元。MPU是單一的一顆晶片,而晶片組則由一組晶片所構成,早期甚至多達7、8顆,但目前大多合併成2顆,一般稱作北橋(North Bridge)晶片和南橋(South Bridge)晶片。MPU是計算機的計算、判斷或控制中心,有人稱它為”計算機的心臟”。

MCU

MCU 微控制單元(Microcontroller Unit) ,又稱單片微型計算機(Single Chip Microcomputer )或者微控制器,是把中央處理器(Central Process Unit)的頻率與規格做適當縮減,並將記憶體(memory)、計數器(Timer)、USB、A/D轉換、UART、PLC、DMA等周邊介面,甚至LCD驅動電路都整合在單一晶片上,形成晶片級的計算機,為不同的應用場合做不同組合控制。諸如手機、PC外圍、遙控器,至汽車電子、工業上的步進馬達、機器手臂的控制等,都可見到MCU的身影。

SOC

SOC的定義多種多樣,由於其內涵豐富、應用範圍廣,很難給出準確定義。一般說來, SOC稱為系統級晶片,也有稱片上系統,意指它是一個產品,是一個有專用目標的積體電路,其中包含完整系統並有嵌入軟體的全部內容。同時它又是一種技術,用以實現從確定系統功能開始,到軟/硬體劃分,並完成設計的整個過程。

DSP

DSP(digital signal processor)是一種獨特的微處理器,是以數字訊號來處理大量資訊的器件。其工作原理是接收模擬訊號,轉換為0或1的數字訊號,再對數字訊號進行修改、刪除、強化,並在其他系統晶片中把數字資料解譯回模擬資料或實際環境格式。它不僅具有可程式設計性,而且其實時執行速度可達每秒數以千萬條複雜指令程式,遠遠超過通用微處理器,是數字化電子世界中日益重要的電腦晶片。它的強大資料處理能力和高執行速度,是最值得稱道的兩大特色。

討論自動駕駛晶片的意義並非單純理解晶片原理,更需要理解計算並非是一個軟體工作而是一個軟硬體配合的工作。很多演算法在不同的晶片上都可以實施,但是量產過程中需要在靈活性以及成本功耗之間做出權衡。而如果要做到這點,你必須理解晶片。

晶片的概念結構

當下晶片結構是複雜的,但簡單劃分就三種概念結構。馮.諾依曼結構,哈弗結構和改進哈弗結構。瞭解一個晶片的結構核心是看它的匯流排佈置和儲存器設計。

打個比方,假如晶片是一個“銀行”,這個銀行很小就兩個人。一個負責撥算盤(計算),其他它都不管。一個負責記錄文件(儲存),把“算什麼?”(資料)和“咋麼算?”(程式)都完整的用文件記錄下來,方便和撥算盤的人溝通。他們之間定義了一個溝通方式(一組匯流排),內容包括了“文件從哪裡取?放回哪裡?”(定址匯流排)和“文件具體內容是什麼?”(資料匯流排)兩大部分,換句話說,一組匯流排包括一個地址匯流排和一個數據匯流排。特別注意這裡的總線上的“資料”對應著一份文件,不要和文件裡 “算什麼?”的這個資料概念混淆了。

客戶把原始的需求文件(包含輸入資料和程式)交給負責記錄的人後,根據定義的溝通方式,和負責實際計算的人一起反覆來回的傳遞文件(拿程式指令,拿資料,返結果),最後把最終的計算結果透過記錄的人反饋給客戶。上面這種分工思路就是馮.諾依曼結構的核心,關鍵的特點就是客戶只用和一個記錄人員溝通就行,再複雜的需求都可以一股腦的給一個人,剩下的都是他們之間的事。整個過程非常靈活,這也是馮.諾依曼結構的最大優勢。這種結構下程式指令儲存地址和資料儲存地址指向同一儲存器的不同物理位置,因此程式指令和資料的寬度相同。但這種方式效率不高,因為記錄的人每個時刻只能幹一件事,要麼告訴撥算盤的人咋麼算,要麼告訴它算什麼。因此出現了哈佛結構,將程式指令和資料分開儲存,指令和資料可以有不同的資料寬度。採用了獨立的一組程式匯流排和一組資料匯流排。這就相當於原來2個人,現在三個人,記錄員分了個工,一個就負責記錄傳遞計算方法(程式),一個人就負責記錄傳遞計算內容(資料)。兩個人和撥算盤的人點對點溝通,但相互之間老死不往來。這種並行化自然提高了效率,原來要至少兩個週期做完的事,一個週期就搞定了。可這種方法讓客戶要同時對應2個毫無聯絡的記錄員這非常不友好。且如果需求側重點不同,兩個人的工作量常常不均衡導致浪費,如果由一個人擔當(馮.諾依曼結構),這些問題都不存在。

為了解決這個平衡問題出現了改進哈弗結構。它只有一組匯流排供程式儲存器和資料儲存器分時共用。原來的哈佛結構需要4條(2組)匯流排,改進後需要兩條(1組)匯流排,且保留了兩個獨立並行的儲存器。也就是說,記錄員還是為了效率做了分工,但溝通方式升級,走上了“敏捷之路”。不再是兩兩溝通的老國企做派,把客戶和撥算盤的人也加入進來做了個四方溝通會(分時公用),歸口統一保證了靈活性,同時分時也對並行化影響不大。

討論完基本的結構思想這裡有幾點要著重提醒下。實際的晶片設計是對這幾種概念結構的擴充套件和巢狀,比如CPU處理器雖然外部總線上看是諾依曼結構,但是由於內部快取記憶體的二級設計,實際上對內已經算是改進哈佛結構了。

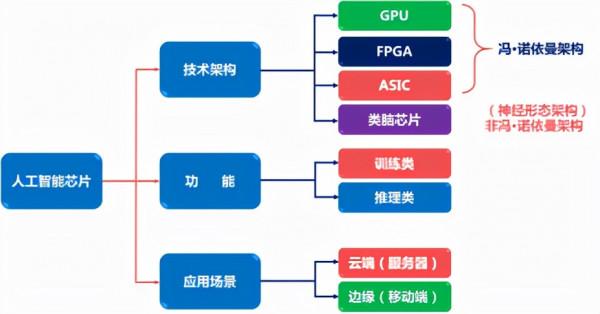

晶片的派系劃分

接著我們聊下晶片的分類,梳理分類首先要區分晶片的兩個大類通用晶片(CPU, GPU, DSP等)和定製晶片(FPGA, ASIC等),這個大類劃分很重要,兩者有本質上的不同。同樣用銀行做比喻,通用晶片就是“銀行櫃員”而定製晶片就是“ATM機”。

通用晶片關鍵是“通用”二字,這意味著其必須具備處理各式各樣千奇百怪的指令要求,並且經常同時存在多個外部裝置的請求,它必須擁有隨時中止目前的運算轉而進行其他運算,完成後再從中斷點繼續當前運算的能力。就好比銀行櫃員,客戶要辦的業務千奇百怪,時常還來個缺德的插隊罵娘或者站著位置不走撩你兩下的人存在。櫃員都要應對。而為了做到這一點通用晶片有複雜的控制取指譯碼流程,Cache記憶體分級機制(緩和高速CPU與低速記憶體的臨時指令儲存器),真正的計算單元ALU只佔了通用晶片不大的一部分,更多設計是為了靈活性存在的,在計算效率和通用性上的權衡上犧牲前者選擇後者。

計算機元件無法理解我們的指令,它們只能理解電晶體實現的兩種狀態:“開”和“關”的含義,對應的就是1和0這,為了讓指令變成CPU能理解的0和1,CPU需要一個專門的譯碼器來翻譯我們的指令。這個過程分為兩步:“取指”(從一個專門存放指令的儲存器中將需要執行的指令提取出來)和“譯碼”(根據特定的規則將指令翻譯成計算單元能夠理解的資料)。

當我們在上文討論晶片結構的時候更多的是在討論通用晶片的結構,是在討論說滿足客戶變化需求的時候,哪種“人員組織形式和溝通方式”是最高效的。

而定製晶片就是完全的另一個概念,雖然它也有結構思想在裡面,但是就像你不會去討論一個程式的“人員組織架構”一樣,在這種晶片里根本就沒有時序中斷,取指譯碼這些為了靈活性而設計的概念。相比通用晶片,定製晶片是沒有“人性”的,就是一個ATM機,其給客戶定義了清晰的操作流程,省去了中斷等大量靈活性設計,撩小姐姐的一套對機器人是不成立。

打個比方,比如一個比大小的邏輯用馮諾依曼結構的CPU至少需要幾條指令完成,但用FPGA就根本不用考慮時序週期,只要串聯幾個邏輯單元,在一個週期就搞定了。但如果再增加幾個邏輯,CPU還是在相同邏輯資源下用幾個指令完成,但是FPGA 就需要額外佔用另一部分邏輯資源完成計算。再比如FPGA和GPU(GPU是通用晶片)在並行化上有類似的思想,但兩者實際沒有多少可比性,你不會把三個櫃員的辦理通道和ATM機理存在在三個恰好並行的流程做比較一樣。還有人在訊號處理效率上把DSP和FPGA拿出來對比,我覺得這些零零種種的比較都沒有太大意義。為靈活性存在的“人”(通用晶片),和為效率存在的“機器”(定製晶片)是兩個維度的事情,不要從效能上去強行比較。

從這裡我們可以大致看出來,兩者的幾個重要差異。定製晶片是對已經固化的業務進行降本增效,就像銀行用ATM機,代替成本更高的櫃員處理一些常規銀行業務。而通用晶片是為了對一些無法或者暫時沒有固化的業務作出的靈活設計。兩者沒有優劣之分。

瞭解了晶片的兩個大方向,我們看下這兩個大方向內部的細分差異以及聯絡。通用晶片下的CPU(MPU), GPU, DSP,MCU之間同樣存在細分差異。

CPU和MPU可以簡單理解為一個概念,只是理解範疇上的區別。CPU和GPU之間的區別更多的是核的數量。CPU雖然有多核,但基本不超過兩位數,每個核都有足夠大的快取和足夠多的數字和邏輯運算單元,並有更復雜的邏輯判斷硬體,就像銀行裡常備的3-4個櫃檯的櫃員,擅長處理客戶很複雜的業務。而GPU的核數遠超CPU每個核擁有的快取大小相對小,數字邏輯運算單元也少而簡單,更像是500多個電話客服櫃員,處理一些相對簡單但數量眾多的客戶業務。

DSP(數字訊號處理晶片)是一類特殊的CPU,採用了上面說的哈佛結構,且存在專用的硬體演算法電路和專門的定址模式。它具有通用晶片設計的靈活性,但在實時運算過程中很少變化,因此特化了業務流程的效能(記錄和計算過程)。就像是某個辦理“外匯存取”的專業櫃檯會部署一些特化的櫃員和流程。DSP對於專用訊號(影片編解碼,通訊訊號)的處理能力遠遠的優於一般CPU。當然普通櫃檯也可以處理展業櫃檯的業務,但價效比就很差了,如果需求很多開設專門的櫃檯就變得有意義,這些還是和客戶需求有關。用DSP處理專門的訊號流常具有執行時間可控,晶片價效比高等優點。

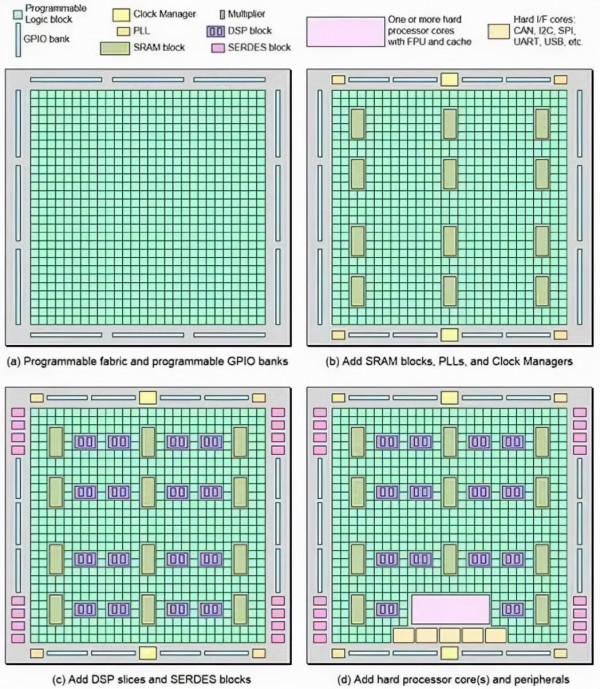

講完了通用晶片,定製晶片也有兩個主要方向,FPGA和ASIC。兩者核心的區別就是固化程度。FPGA仍然具有一定的靈活性(但遠遜於通用晶片),而ASIC則是完成固化的設計(也存在和FPGA類似的部分編輯的產品存在)。類似可以程式設計的ATM機和完全固化的ATM機,兩者區別最大的維度還是成本和功耗。

FPGA最早是從專用積體電路發展而來的半定製化的可程式設計電路,是高階的CPLD (Complex Programmable Logic Device複雜可程式設計邏輯器件)。FPGA可以實現一個DSP, GPU甚至是CPU的功能,就像之前說的把櫃員業務固化為ATM機操作流程一樣。但不是說FPGA可以代替CPU,這是設計目的上的大方向差異,反覆強調。

FPGA是一堆邏輯閘,透過硬體描述語言HDL把它轉成電路連線,從最基本的邏輯閘層面上連線成電路。雖然看起來像一塊CPU,其實是完全硬體實現的。根據一個固定的模式來處理輸入的資料然後輸出。FPGA片上大部分都是計算單元,沒有控制單元並不代表FPGA不會執行指令,事實上FPGA裡控制單元的角色由單元和單元之間可程式設計邏輯連線線來完成的,透過HDL程式設計更改每個單元的運算邏輯和單元之間的連線方式,從而使其達到和一般的執行程式差不多的效果。由於省去了CPU的取指和譯碼兩個步驟,FPGA重複執行相同程式碼的效率得到了極大的提高,也因此,其無法應對沒有被程式設計過的指令。

ASIC就是專用IC,沒有明確的定義。可以理解為除了微控制器、DSP、FPGA之類的能叫出名的IC,剩下的都是ASIC。ASIC原本就是專門為某一項功能開發的專用整合晶片。後來ASIC發展了一些,稱為半定製專用積體電路,相對來說更接近FPGA,甚至在某些地方,ASIC是個大概念,FPGA屬於ASIC的一部分,也常常被作為ASIC開發的預研。其代表了在需求一定的情況下,對價效比的極致追求。

晶片之上的整合

在上面我偷偷遺漏了一個概念MCU,原因是其本身不是一種晶片型別而是一種整合方式,SOC晶片也是同樣的道理,兩者的區別是程度上的不同。在自動駕駛汽車領域MCU更多的是集成了更多的輸入和輸出裝置在晶片當中,方便更好的控制,因此叫做微控制器而不是微處理器。而SOC是在更高的層面上將不同的晶片做了進一步的整合,維度更高。如果MCU是一種人員組織最終形成一個公司對外服務,那SOC更像是公司級別的組織形成了一個行業對外服務。

微控制器是MCU的通俗說法,經典的51系列就是一堆IO口,後來慢慢的把常用的PWM, AD之類的功能加入了微控制器之中。其構成等價於一個帶了更多外設CPU,但側重點是討論其外設的部分。在PWM,AD等之上繼續發展其外設也就形成了汽車行業熟悉的ECU即電子控制單元,同時泛指汽車上所有電子控制系統,可以是轉向ECU,空調ECU等。

ECU一般由MCU,擴充套件記憶體,擴充套件輸入和輸出(CAN/LIN,AD,PWM等),電源電路和其他一些電子元器件組成,特定功能的ECU還帶有諸如紅外線收發器、脈衝發生器,強弱電隔離等元器件。整塊電路板設計安裝與一個鋁質盒內,透過卡扣或者螺釘方便安裝於車身鈑金上。

在輸入處理電路中,ECU的輸入訊號主要有三種形式,模擬訊號、數字訊號(包括開關訊號)、脈衝訊號。模擬訊號透過A/D轉換為數字訊號提供給微處理器。

在輸出電路中,微處理器輸出的訊號往往用作控制電磁閥、指示燈、步進電機等執行件。微處理器輸出訊號功率小,使用+5v的電壓,汽車上執行機構的電源大多數是蓄電池,需要將微處理器的控制訊號透過輸出處理電路處理後(D/A,放大等)再驅動執行機構。

電源電路中,傳統車的ECU一般帶有電池和內建電源電路,以保證微處理器及其介面電路工作在+5v的電壓下。即使蓄電池電壓有較大波動時,也能提供穩定電壓保證系統的正常工作。

一般搭載8位MCU的ECU主要應用於風扇控制、空調控制、雨刷、天窗、門控等較低階的控制功能。16位MCU主要應用如引擎控制、齒輪與離合器控制等。32位MCU應用於多媒體資訊系統,實時性的安全動力系統以及複雜的X-by-wire等傳動功能。更復雜的功能就不在MCU或者ECU的討論範圍內了。

隨著自動駕駛的發展,ECU的概念進一步升級,更為流行的說法是域控制器,其無外乎就是把MCU變成了SoC(片上系統),同時集成了更多的外圍裝置而已。目前域控制器搭載的主流通用晶片(GPP)多采用SoC的晶片設計方法,透過HDL語言在SoC內由電路整合各種功能晶片。在SoC中各種元件(IP核)採用類似搭積木的方法組合在一起。IP核(諸如典型的ARM核心設計技術)被授權給數百家半導體廠商,做成不同的SoC晶片。還可能整合GPU、編解碼器(DSP)、GPS、WiFi藍芽基帶等一系列功能。如果看一下高通或者TI的晶片,基本是一個ARM核控制整體運算,一個DSP處理語音編解碼, 一個GPU負責影象運算,一個基帶和天線處理模組負責通訊,以及GPS,安全加密等林林總總的特殊晶片。

過去極端情況下自動駕駛的原型處理器功耗可以高達5000W,不僅昂貴且需要搭載額外的散熱裝置。SoC和ASIC的發展給我們帶來很多啟示,回到我經常提及的貫穿整個自動駕駛系統的靈活性。在新的SoC世界裡,你不會從不同的供應商那裡組裝物理元件。相反,你從不同的供應商那裡組裝IP從而獲得更好的整合度,也因此更容易降低功耗和成本。

軟硬體的匹配設計

大部分自動駕駛演算法公司都想定製或自制ASIC/SOC計算平臺,原因還有另一個層面來源於軟硬體的匹配問題。演算法的效能與硬體設計往往脫離不開。追求模組化就要犧牲利用率。要提高利用率就需要軟硬體一體設計。你的演算法是用GPU合適還是CPU合適,網路模型一次用多少記憶體又同時使用多少MAC,由此來設計晶片。或者說反過來給定一個晶片,我的演算法要如何相容,是否要減少記憶體訪問次數提高利用率,還是要遷移部分CPU基於規則的演算法,改為用GPU基於深度學習來實現。軟硬體一起考慮往往才能充分利用好系統性能。

不同的晶片,不同的演算法和需求,往往有最優的組合方式。比如一個經典底層而常用的演算法應用,需求是大量的且競爭是激烈的時候,ASIC就是很好的選擇。為了一個簡單功能(比如編解碼)支付一個ARM的授權是愚蠢的。

如果演算法非常經典且底層,但仍然有改進的空間和需要適配的不同場景,訊號流的處理(手機語音處理)可以直接使用DSP,而更復雜的輸入輸出邏輯演算法(比如影象SIFT特徵處理),就可以交給FPGA來做,效能相對於CPU都可以由30-100倍的提升,且成本和耗能更小。

在複雜演算法領域相對於CPU,GPU的眾核架構把同樣的指令流並行傳送到眾核上,採用不同的輸入資料執行。所以GPU比CPU更適合並行演算法,而序列的複雜規則邏輯則更適合CPU處理。更具體的說,如果標量視為零階張量,向量視為一階張量,矩陣視為二階張量。CPU對應標量計算,主要是路徑規劃和決策類演算法,常用的感測器融合如卡爾曼濾波演算法也多是標量運算。GPU則對應向量或者說向量計算,包括點雲,地圖,深度學習,核心是矩陣運算。用CPU編寫程式時,更適合透過精益化邏輯來提升效能。而用GPU編寫程式時,則更合適利用演算法併發處理來提升效能。

以上,對晶片的理解到這個程度一般工作就能夠開展了,如果對自動駕駛感興趣,歡迎關注我的公眾號。

--END--

關注《無人駕駛俱樂部》,讓你更懂汽車無人駕駛技術!

歡迎加入《無人駕駛俱樂部》!

2021:共同學習、共同進步、共同發展。

智慧駕駛ADAS,V2X, 感知融合!