最近發生不少值得探討交流的事情,譬如 Intel 終於短痛 RKL,蓄力發了個大招 ADL——12代酷睿。相比拉了大胯的上一代,12代酷睿 ADL 確實能擔大任,有望拯救 Intel 消費級的口碑,下面慢聊。

雖然 新聞解禁 時間是10月28號0點 ,但 效能測試 的解禁時間是下個月初,為了保護訊息來源,這裡不會在效能測試解禁前 非常明確 地說明任何一款 ADL 處理器的效能表現。

本文非 Intel 或任何一方利益相關廠商邀稿,會在儘量保持中立的前提下,結合客觀事實,帶來正面與負面的主觀判斷與評價,歡迎拍磚但請禮貌。

新特性一:大小核混合架構

在2020年 Intel 已經嘗試過“混合式”的大小核 CPU佈局,LakeField 就是試水之作,1顆 Sunnny Cove 大核,4顆 Tremont 小核。

但最終 LakeField 產品線中如 i5-L16G7、i3-L13G4 ,體現在如 三星 Galaxy Book S 或 聯想 ThinkPad X1 Fold 這些終端裝置上,基於 Windows 10 x86 的效能排程表現並不如人意,理解成“積累經驗”也不為過。可能也就這幾家日子過得好的OEM才有心思上來湊合。

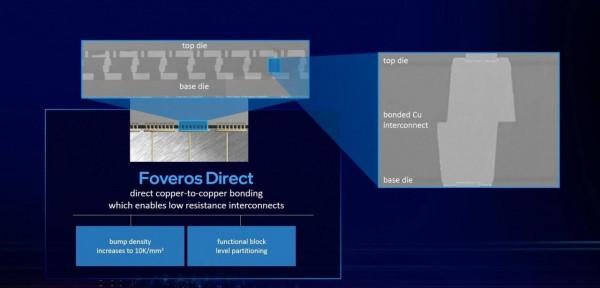

排除坎坷試水,LakeField 更值得世人關注的點,大概是助力更高整合度的 Foveros Die to Die Interface (FDI) 技術,這裡暫且放下,有興趣可自行了解。

區別於 LakeField 對低功耗、高整合的探索,AlderLake 的目標是追求效能,目前最高規格的i9-12900K,由8顆 Golden Cove 以及 8顆 Gracemont,在同一枚封裝中實現。其中P-Core(效能)Golden Cove 可開啟HTT超執行緒,所以規格為8C/16T,E-Core(能效)Gracemont 不具備HTT技術,規格為8C/8T,故i9-12900K的核心執行緒規格為8P+8E=16核心、16+8=24執行緒,即 16C/24T。

其他規格:i7為“8P+4E”,i5為“6P+4E”。

新特性二:告別14nm,製程節點升級

今年7月的架構日上,在高調宣佈自己要進入“IDM 2.0 時代”後,Intel 對自家的製程節點命名做出了變更。

Intel 10nm ESF 與 Intel 7nm,分別改成了Intel 7 與 Intel 4,再往下還有Intel 3, Intel 20A。此番更改頗有向三星半導體與臺積電以直報怨的味道,這是說得通的,只是在理論上這是否算晚了十幾年呢?—— 22nm FinFET 的 Haswell 時代早該先破再立,可偏偏等到2021。

此次12代酷睿 AlderLake 使用的製程節點為 Intel 7,也就是之前一直說的 Intel 10nm Enhanced SuperFin (10nm ESF),桌面端消費級CPU終於擺脫14nm無盡的+++,進入了10nm製程節點。

ADL 與 SPR

本次製程提升在物理意義上有顯著改變,但也有一些不變的地方,下文細說。

新特性三:硬體執行緒排程器

Intel Thread Director 也是前幾個月在PPT裡講過的點,但個人不認為這對AMD Ryzen CPPC 2.0 技術有什麼針對的意味,僅僅是為滿足自己需求而做的東西。Intel 宣稱在 LakeField 就已試驗過它的早期版本,Thread Director 在 AlderLake 是基於硬體的,根植於架構當中。

“英特爾硬體執行緒排程器完全是一個硬體功能,這個硬體功能是內嵌在CPU架構當中的。 那麼它如何工作呢?它是和作業系統配合工作的,比如說以Windows 11為例,Windows 11啟動的時候,能讀CPU ID,比如說它讀到一個12代的核,它就能夠知道12代的核會有英特爾硬體執行緒管理器的功能。”

“OS做一件事,就是在記憶體當中開一塊專有空間,這塊專有空間是一個數據列表,這個資料列表是由核裡的英特爾硬體執行緒排程器來動態更新和管理的。 除此之外,在核的內部會有硬體暫存器,暫存器會表述這個核本身的特性和這個核上執行的任務的分類。比如說這個特性是說高效能核還是高能效核,任務上分類是哪幾種。基於OS所開拓的在記憶體當中的列表和每個核上暫存器列表的對應,這樣Windows 11就知道在不同的應用,不同的執行緒應該被放到哪些核上。這是英特爾硬體執行緒排程器和Windows 11相配合來完成核資源的調配和最佳化。”

-Guy Therien

新特性四:DDR5 & PCIe 5.0

對DDR5的支援在大多數人預料之中,不過目前 Z690 晶片組主機板平臺同時支援 DDR4/DDR5 兩種記憶體,主機板OEM廠商偏好將高階 Z690 型號規劃為DDR5支援,中低端則是DDR4,當然商業規律並不絕對,技術上並無高低端之分。

相對已經無比成熟的DDR4記憶體,DDR5初期會有很多區別體現在行業與具體產品上,對玩家的影響更多關於DDR5記憶體的資訊,下文詳敘。

對這塊並不太關注的玩家,可能會覺得詫異:我PCIe 4.0還沒捂熱呢,怎麼就5.0了?別太在意,目前應用情景還比較狹窄,且在MSDT如Z690這種平臺上,通道拆分還是比較束手束腳的,在拆分自由度上並沒有進步,只不過代數更迭提升頻寬而已。

(Intel:AMD首發4.0讓我們很被動,這樣下去肯定是行不通的,必須首發個5.0還一手)

從14nm+++到10nm ESF

Intel 家的 Foundry 有一種很成熟的製程節點工藝,相傳叫作14nm。現在是早已併產線一起遺忘到故紙堆裡去了,雖然那最末次的相見才隔了半年,其中似乎確鑿只有十一片矽渣;但那地方卻是我的歡樂源頭。

——《從14nm+++到10nm ESF》

改編不是亂編,如今確實不該叫 10nm ESF,要叫 Intel 7。

按邏輯順序,要談的問題很多,先從製程節點本身開始。前面有提到製程,吐槽了一句“22nm FinFET 的 Haswell 時代早該先破再立”,大致道理是 Intel 在 Haswell(4代酷睿)時領先業界使用了基於 22nm 節點的 FinFET 技術,與上一代 32nm Sandy Bridge 的 Planar FET 有很大不同:

前置補充:

Planar FET 時,衡量“幾納米制程”的標準確實是柵極下的溝道長度,柵極控制溝道狀態,更短柵極意味著更大電流或者更小電壓,它對於通道的控制水平代表這枚電晶體的效率。

但當這個尺度縮小到32nm,也就是3代酷睿 Sandy Bridge 時,以當時的離子注入工藝水平,很難再防範量子隧穿效應,繼續削薄柵極減短溝道長度十分困難。

所以想要進一步減短溝道距離同時降低漏電率,Planar FET 前路無幾,於是從 22nm Haswell 另闢蹊徑 FinFET,不同於 Planar FET,FinFET 的源極與漏極被塑形為立體的片狀。

為什麼是片狀?因為柵極控制源極與漏極之間的通路,作用意義可比擬為閥門,開就是1,合即是0,Planar FET 柵極控制通路的接觸只有一面,而鰭式場效應電晶體的立體結構則有三面,電流傳輸通路的橫截面變大,電阻更小電流更大,控制能力提升。同時,用異質外延做源極與漏極,直接從柵極上“生長”出來但被隔開,可進一步削薄柵極,減短溝道距離。

FinFET 繼續縮柵極,各部位尺寸的縮小卻並不能跟上,此時舊標準不再適合準確衡量制程的先程序度,但三星半導體(主要就是這位)、臺積電、格羅方德選擇繼續這種說法,並在宣傳上朝著對自己有利的方向加工。

時過境遷,10nm 先進製程賽道上,兩位玩家“5nm”、“3nm”叫喊聲此起彼伏,欄杆外的 Intel 百感交集,終究選擇“從善如流”。所以錯的是誰呢?或許誰都沒錯,但輿論上一定有輸家,是誰我不說。

回到 10nm ESF——Intel 7 的話題上,降維到具體的產品如酷睿 i9-12900K,新制程實在地體現在了晶片的封裝面積上:

相比狹長的10900K 與碩大的11900K,10nm 的 12900K 核心面積回到了正常狀態,與10900K 相仿,不僅如此還進一步加厚了 IHS (頂蓋),再次削薄了 Die,這些舉措對散熱都有幫助,具體數值屬於效能測試部分暫不能說,可以說遊戲環境下近似10代 CML 的水平。

這是Intel官方圖,僅作示意,並不完全準確,未體現基板厚度變化

這是Intel官方圖,僅作示意,並不完全準確,未體現基板厚度變化

但這種偏長的封裝以及 LGA 1700 的尺寸,還是對散熱器提出了要求(功耗詳見前兩代並沒有降低),儘管不少 Z690 主機板都有做對 LGA 1200 散熱安裝孔的相容,但同時還需注意的是AIO(一體水冷)冷頭安裝方向,會帶來明顯溫度差異。

“五”限前瞻?

DDR5

PCIe 5.0

可以直接引用 Intel 官方在 10.26上午 的 ADL-S產品技術解析會上的 Q&A。

Q23:記憶體DDR4和DDR5效能的區別是什麼?

Wilson Lee答:

我們對遊戲效能的測試確實在DDR4和DDR5上都做了比較廣泛的測試,我們測試的比較有代表性的30多款遊戲之下看到的是總體來說DDR5的效能還是好過DDR4,當然有一些問題我就不具體贅述了,可能大家會覺得DDR4的延遲好過DDR5,DDR5的頻寬好於DDR4。

今天看到比較好的SPEC的這些DDR5的記憶體確實有這樣的情形。但是總體而言,遊戲效能還是DDR5好過DDR4,平均下來,從我們測過的30多個遊戲來看,他們兩者的遊戲效能差別是小於5%的,也就是說是一個比較小的差別。當然在具體遊戲上,也有大過5%的差別的,這個要就事論事看,具體遊戲來說,總體而言差別不大。

官方回答值得信任,但他們也留了一點東西沒說。其實 ADL 這一代,因為架構區別(雙架構IMC),以及現階段大小核排程難以避免的損失,同條件下的 DDR4 延遲是要高於 RKL DDR4 的,官方當然不會細緻入微提及,畢竟最常見吃記憶體延遲的遊戲情景有長足進步,但事實即是如此。如何破解呢?如果有純大核的 ADL 似乎可解。

還有些其他資訊,比如 DDR5 眾所周知目前顆粒都是16Gb,所以單面8顆粒的DDR5 UDIMM 就是16GB一條了,雙面則是32GB。單面的 PoR Intel 給了 4000MHz(4DIMM 插滿),雙面則是 3600MHz(4DIMM 插滿),但玩家也不用太當回事,畢竟這是 Intel 給的PoR,而非OEM最終的調校。

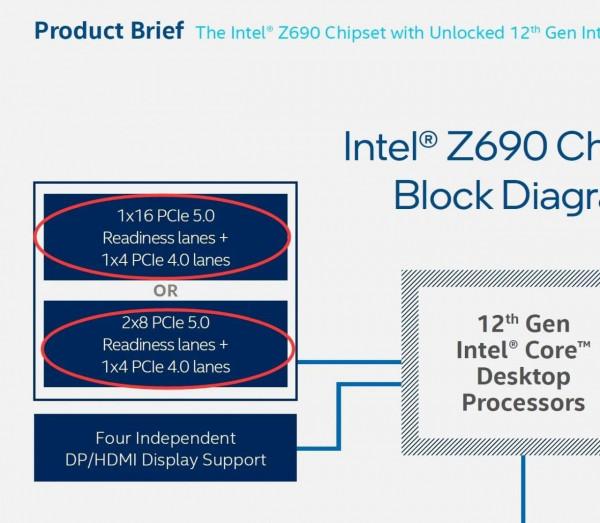

而對於 PCIe 5.0,個人觀點是5.0/4.0並不那麼重要,重點在於PCIe通道切分的細緻度,Intel Z系晶片組主機板的PCIe切分策略,多年以來有例在先——平穩提升,並不激進。

與本次 Z690 作對比,下面放 Z490 Z590 晶片組拓撲圖(區域性):

Z490: [16+0+0], [8+8+0], [8+4+4]

Z590: [16+4+0], [8+8+4], [8+4+4+4]

Z690: [16+4+0], [8+8+4]

相比上一代,對於直連 CPU 的 PCIe 通道,Z690 的做法似乎有點“倒吸”——當然,對於絕大多數使用者而言,這並沒什麼影響。

Victor Ju:

總的來說,我們希望推進行業向前發展,但是發展程序當中,我們也會關注現有產業鏈的狀態,做到既不激進也不保守。

希望英特爾能切實做到這一點。

一些別的

暫時阻礙 AlderLake 成為大家心目首選的,我認為有以下幾點:

Z690 主機板初期高價

需要從兩個角度看問題:

首先,一種新的晶片組主機板發售前幾周,必然存在溢價,更別提Z系屬於MSDT平臺中最高階的晶片組;

其次,Z690 主機板的 DDR5 型號,在記憶體訊號佈線、供電保護等環節需要下更多成本。

看看某品牌 旗艦Z690主機板 將近15000的售價,12代酷睿CPU本身倒不見得有多貴了。

DDR5 記憶體初期高價

其實 Intel 也並不掩飾:相對 DDR4,DDR5 在遊戲測試中並不見得搶太多風頭。但其他領域如何?當然還得等 下月4號晚間 的效能測試解禁咯。

DDR5 記憶體初期在市場上的各種型號,確實是良莠不齊的,如果要去挖問題源頭,Intel 又要自食其果接一部分鍋:

JEDEC一言不合就開擺為哪般?

記憶體模組廠攬了挺大一部分板廠記憶體調校的活,為啥同時也不見板廠能多輕鬆?

某些記憶體模組型號用的PMIC真爛到感人,誰去管管呢?

競爭對手的路線

在對應市場上 Intel 只有一個競爭對手 —— AMD。在經歷了10代 CML 與11代 RKL 被對面銳龍 Zen3 VMR 連幹兩代、殺到顏面掃地之後,Intel 12代酷睿 ADL 終於全面反攻成功,在效能上重回冠軍寶座。

但,價格呢?消費者可是用腳投票的,在愈發艱難的年頭,沒人用血汗錢開玩笑,誰都知道 B560 開始的英特爾B系主機板變更香了,

雙十一是不錯的觀察視窗,消費者有機率見到 AMD 的應對策略,聯合OEM廠商降價出清免不了——昨天上午AMD中國可是喊了一大群OEM開會。

AMD銳龍接下來的路線,我認為是穩步提高 B550主機板 以及 Zen3 CPU 的普及率,然後在2022基本躺平,2022年底用 Zen4 想辦法翻身——具體情況談還太早,一切都沒定論。

顯然,如果Z690主機板能便宜,DDR5記憶體能便宜同時儘量保證質量與效能,ADL 在2022的推開是幾乎不會遇到阻力。