垂直奈米環柵電晶體因其在減小標準單元面積、提升效能和改善寄生效應等方面具有優勢,可滿足功耗、效能、面積和成本等設計要求,已成為2nm及以下技術節點晶片的重點研發方向。

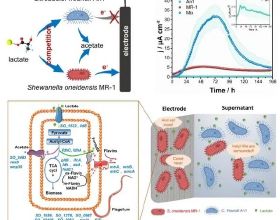

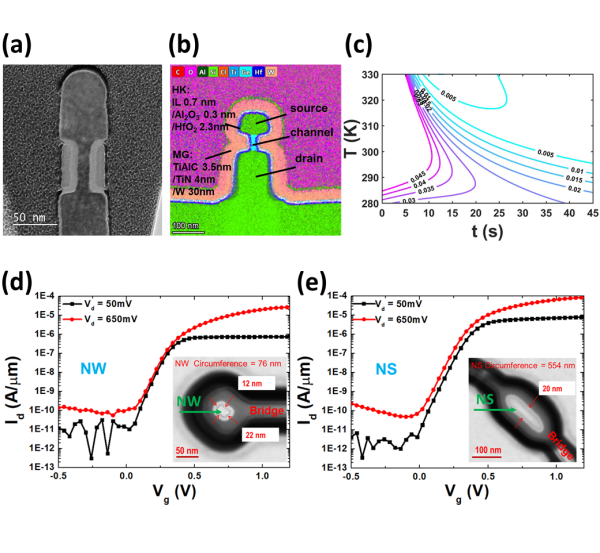

中國科學院微電子研究所積體電路先導工藝研發中心研究員朱慧瓏團隊研發出p型具有自對準柵極的疊層垂直奈米環柵電晶體(IEEE Electron Device Letters,DOI: 10.1109/LED.2019.2954537,2019),並剖析n型器件。與p型器件製備工藝不同,n型器件在外延原位摻雜時,溝道和源漏介面處存在嚴重的雜質分凝與自摻雜問題。為此,團隊開發出適用於垂直器件的替代柵工藝,利用假柵做掩模透過離子注入實現源漏的摻雜,既解決了上述外延原位摻雜難題,又突破了原位摻雜的固溶度極限,更利於對電晶體內部結構的最佳化和不同型別電晶體之間的整合。

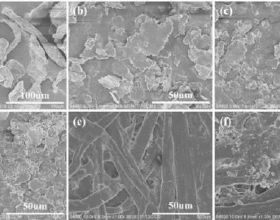

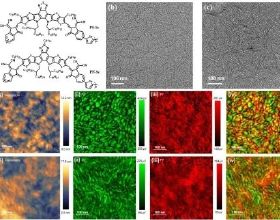

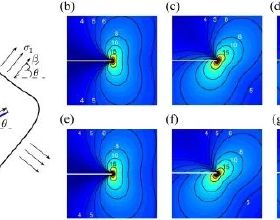

為獲得可精確控制溝道和柵極尺寸的垂直環柵器件,選擇性和各向同性的原子層刻蝕方法是關鍵工藝。科研團隊對該方法開展了深入分析和研究,提出了相應的氧化—刻蝕模型,應用於實驗設計,改進和優化了橫向刻蝕工藝;用該刻蝕工藝與假柵工藝結合,製備出具有自對準柵的n型疊層垂直奈米環柵電晶體,器件柵長為48奈米,具有優異的短溝道控制能力和較高的電流開關比(Ion/Ioff),奈米線器件的亞閾值擺幅(SS)、漏致勢壘降低(DIBL)和開關比為67 mV/dec、14 mV和3×105;奈米片器件的SS、DIBL和開關比為68 mV/dec、38 mV和1.3×106。

相關研究成果發表在Nano Letters(DOI:10.1021/acs.nanolett.1c01033)、ACS Applied Materials & Interfaces(DOI:10.1021/acsami.0c14018)上。研究得到中科院戰略先導科技專項(先導預研專案“3-1奈米積體電路新器件與先導工藝”)、中科院青年創新促進會、國家自然科學基金等的資助。

(a)替代柵結構TEM截面,(b)垂直環柵奈米器件TEM截面的EDX元素分佈圖,(c)氧化-刻蝕模型,(d)n型垂直環柵奈米線器件的Id-Vg特性及TEM俯視插圖,(e)n型垂直環柵奈米片器件的Id-Vg特性與TEM俯視插圖。

來源:中國科學院微電子研究所