基於二維材料的場效應電晶體在超大規模積體電路(VLSI)技術中具有廣泛的應用潛力,但它們是否可以在生產線前端或後端透過單片整合或異質整合長久以來仍然是懸而未決的問題。要實現這一目標,不僅需要克服包括降低接觸電阻、開發穩定可控的摻雜方案、推進遷移率工程和改進高κ介電整合在內的多重挑戰,還需要能夠大面積生長均勻的二維層,以確保二維場效應電晶體低缺陷密度和無懸掛鍵的介面。

近期,由來自美國賓夕法尼亞州立大學Saptarshi Das教授領導的國際研究團隊,在電子學國際著名期刊Nature Electronics上以Transistors based on two-dimensional materials for future integrated circuits為題發表綜述文章,系統回顧了用於未來超大規模積體電路技術的二維場效應電晶體的發展,討論瞭如何提取和評估這些二維電晶體的關鍵效能指標,並展望了二維電晶體在微納電子學、神經形態計算、高階感測、資料儲存和未來互連技術中的潛在應用。

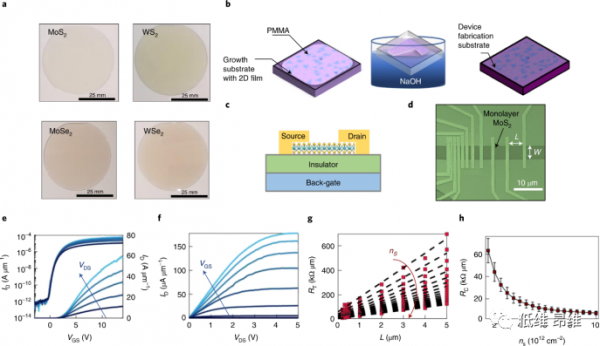

圖1.二維場效應電晶體的製備和表徵。

圖源: Nat Electron 4, 786–799 (2021).

目前,矽互補金屬-氧化物-半導體(CMOS)技術的規模已經達到了10奈米以下的技術節點,但因為10奈米一下器件的柵極靜電要求大幅減小溝道厚度以保持所需的效能,所以進一步的規模化越來越具有挑戰性。未來,場效應電晶體的最終溝道厚度可能在亞1奈米範圍內。然而,這對於任何三維半導體晶體來說都是不容易實現的,因為在溝道-電介質介面處電荷載流子的散射增加,這會導致嚴重的遷移率退化。

單層形式、厚度約為0.6 奈米的二維半導體材料,可以為此問題提供一種解決方案。這種材料包括通式為MX2的過渡金屬二鹵化物(TMD),其中M為過渡金屬(例如,Mo或W),X為硫族元素(例如,S、Se或Te)。材料中不存在懸空鍵也有助於實現更好的溝道-電介質介面。早期學術界基於機械剝離的單晶二維薄片的研究,以及最近基於大面積生長的合成二維單分子膜的發展,都說明了二維電晶體的優異特性。然而,許多有待解決的挑戰使得二維場效應電晶體在未來超大規模整合技術中的應用前景還很不明朗。

在這篇綜述中,研究人員探討了未來積體電路中二維場效應電晶體的發展。文章首先考慮二維溝道材料的大面積生長和二維場效應電晶體的製造,以及關鍵引數的提取,以全面評估器件效能。然後,文章分析了研究二維場效應電晶體的器件間變化、穩定性和可靠性的重要性。接著,文章評估了實現基於二維場效應電晶體的超大規模整合應用必須解決的關鍵挑戰,如降低接觸電阻RC、實現穩定摻雜、推進遷移率工程和改進高κ電介質(其中κ是介電常數)的整合。最後,文章重點介紹了二維場效應電晶體在數字和類比電子學、儲存器、神經形態計算、感測器件和互連技術中的潛在應用。

二維材料加工基礎

二維場效應電晶體的最早是基於微觀機械剝落薄片實現的。儘管機械剝離技術缺乏可擴充套件性和可製造性,但它可以實現不同二維材料的快速實驗篩選,並作為裝置最佳化和應用的試驗檯。它還有助於檢查二維材料與標準加工技術的相容性。然而,對於二維場效應電晶體的超大規模整合而言,晶圓級合成是不可避免的,化學氣相沉積(CVD)和金屬-有機CVD技術是這方面的先驅。圖1a顯示了有機CVD在兩英寸藍寶石晶圓上生長的MoS2、MoSe2、WS2和WSe2。雖然最重要的生長引數是工藝溫度,通常大於500 °C時,前體和基質的選擇也會影響生長。例如,諸如藍寶石的晶體襯底可以促進過渡金屬二鹵化物的外延生長,這大大減少了晶界的數量並改進了二維場效應電晶體的效能。請注意,二維場效應電晶體必須滿足裝置和系統國際路線圖(IRD)規定的效能標準,以作為高階節點中的前端(FEOL)裝置,如下文所述。後端(BEOL)裝置的效能標準不那麼嚴格,但CMOS工藝相容性需要低溫生長(<450 °C)的過渡金屬二鹵化物,這是非常重要的,除了一些初始演示之外,還需要進一步的調查。或者,單片整合的溫度和襯底相關限制可以透過在具有更高熱預算的所需襯底上生長過渡金屬二鹵化物來避免,隨後是乾淨且無損傷的大面積傳輸。圖1b顯示了目前學術界已經開發的常用的溼轉移技術。

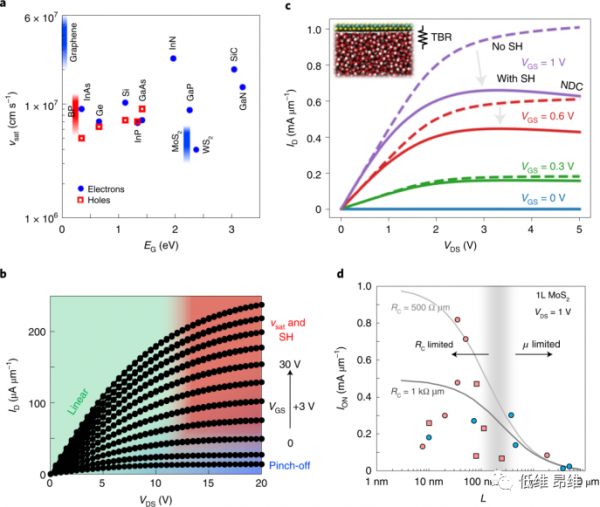

圖2.二維場效應電晶體中的飽和電流和飽和速度。

圖源: Nat Electron 4, 786–799 (2021).

二維場效應電晶體在未來超大規模積體電路中的潛在應用

二維場效應電晶體提供了廣泛的潛在超大規模積體電路應用,文章討論了二維場效應電晶體在包括傳統的微納電子學、三維整合、人工智慧硬體、銅互連的感測和擴散屏障替換等方面的應用。

微納電子學

二維場效應電晶體可用於標準數字邏輯、類比電路和射頻(RF)電子學,以及各種易失性和非易失性儲存器裝置中的有源和無源元件,包括靜態隨機存取儲存器(SRAM)、動態隨機存取儲存器(DRAM)和浮柵儲存器(FG)。

對於數字邏輯閘,主流工業界認為到2028年,節點需要約0.78ps的切換延遲和~0.47 fJ的開關能量。此外,對於HP和LP IRDS節點必須分別保持關閉電流IOFF為10 nAµm-1和100 pAµm-1來限制靜態功率。在此背景下,二維場效應電晶體在匹配甚至超越矽場效應電晶體方面顯示出巨大潛力。除了單個器件外,二維場效應電晶體的電路級演示還包括微處理器、模擬運算放大器和靜態隨機存取儲存器單元。基於二維場效應電晶體的超大規模整合的一個關鍵考慮因素是器件-電路協同最佳化。例如,可以透過減小互連線尺寸來降低接觸電阻的主要影響,並且可以透過最佳化背柵極重疊來降低雙柵極架構增加的功耗。

除了幫助CMOS邏輯擴充套件外,二維電晶體還可以改善記憶體擴充套件。六電晶體靜態隨機存取儲存器及其更大版本的暫存器檔案是邏輯晶片中的主要儲存元件。由於它們基於邏輯技術電晶體,二維場效應電晶體為CMOS所展示的任何縮放、效能和洩漏優勢都將直接反映在二維 靜態隨機存取儲存器的特性上。事實上,基於具有三層結構的二維場效應電晶體的靜態隨機存取儲存器設計表明,在未來節能計算系統中,每單位面積的儲存容量有了大幅增加。二維場效應電晶體作為動態隨機存取儲存器存取電晶體也是非常有潛力的方向,因為它們可以比矽場效應電晶體更好地擴充套件,同時保持低洩漏和可比的通電狀態。各種非易失性儲存器,例如浮柵儲存器,它們是在電子產品中保留大量資料的關鍵,可以使用二維場效應電晶體來取代目前使用的低遷移率和較差的亞閾值斜率多晶矽NAND電晶體。然而,這將需要在極高縱橫比通孔的側壁上以較低的熱預算生長二維通道。氧化物側壁上過渡金屬二鹵化物溝道生長的良好進展已被證明,但電晶體效能和可擴充套件性需要進一步改進。新興儲存器,如鐵場效應電晶體,提供更好的縮放和高速操作,也可以利用二維通道。除了記憶體和邏輯,二維場效應電晶體還可用於射頻電子裝置、硬體安全以及柔性顯示電子裝置。

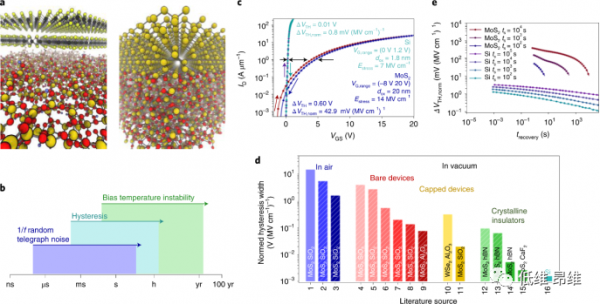

圖3. 二維場效應電晶體的可靠性與穩定性。

圖源: Nat Electron 4, 786–799 (2021).

三維整合

三維單片整合為半導體工業的未來提供了一條潛在的道路。根據IRDS 2020報告,預計到2034年,“More Moore”要求 由四個垂直堆疊的奈米片組成的“07 nm eq node”柵極長度為12 nm,,奈米片厚度為5 nm。透過這種方式,靜電門控制可以保持,同時實現每個封裝外形上可接受的電流水平。二維材料的原子薄特性使層間訊號延遲低,散熱更容易,與傳統單片三維整合相比,整合密度高出150%以上。這種二維材料還提供良好的靜電遮蔽和高頻電場遮蔽,這對三維整合非常重要。因此,三維整合雙柵WS2場效應電晶體在滿足3奈米鰭式場效應電晶體節點的要求方面具有潛力。類似地,在三維多通道MoS2場效應電晶體中實現了高驅動電流。此外,基於環柵 MoS2場效應電晶體的環形振盪器電路在IMEC 2-nm節點上顯示出優於矽基環柵器件的潛力。已經使用MoS2和WSe2場效應電晶體的三維單片整合演示了數位電路元件,如反相器、NAND和NOR元件,以及模擬元件,如差分放大器、共源放大器和訊號混頻器。類似地,全WSe2 單電晶體單電阻隨機存取儲存器單元已證明二維材料用於三維嵌入式儲存器的潛力。請注意,儲存器和邏輯的單片三維整合是一種很有希望的替代方案,可以滿足人工智慧和機器學習工作負載對記憶體內和近記憶體計算的日益增長的需求。三維整合也可用於在同一晶片中實現多功能器件。例如,用於影象感測應用的MoS2光電電晶體陣列已整合在基於多晶矽奈米線場效應電晶體的三維積體電路之上。事實上,二維材料可用於製造大規模電晶體、密集儲存單元和感測元件,為其三維整合提供了多種機會。

電路互連

二維材料也可以在互連技術中找到潛在的應用。隨著目前積體電路中的每個技術節點都要求銅互連變得越來越緊湊,這不可避免地會導致矽晶片中電阻-電容延遲的增加。由於銅的電阻率隨著側壁和晶界散射的增加而迅速增加,因此在超尺度尺寸下,這個問題變得更加嚴重。此外,眾所周知,銅很容易擴散到周圍的電介質中,特別是在大電場下,這就需要使用擴散屏障。通常使用由氮化物(TiN或TaN)基擴散阻擋層和耐火金屬(Ta或W)基襯墊組成的雙層堆疊。因為這些材料比銅的電阻大得多,所以它們的厚度需要儘可能薄,以實現整體低線電阻。然而,當這些阻隔材料的尺寸非常大時,它們就失去了阻止銅擴散的能力。因此,在不久的將來,超大規模互連迫切需要亞奈米級勢壘解決方案。實驗和模擬都表明,石墨烯、hBN和各種過渡金屬二鹵化物等二維材料可以成為銅的有效擴散阻擋層。例如,在銅電極和底層電介質襯底之間插入單層MoS2可顯著提高器件可靠性和效能。為了實現這些二維材料作為互連技術潛在的亞奈米薄勢壘解決方案,有必要在後端(BEOL)相容溫度下生長高質量的二維勢壘。最近的研究表明,鉭在後端(BEOL)溫度下成功地轉化為二維 TaS2阻擋層,作為優良的銅擴散阻擋層和粘附襯層,可提高銅互連的效能。除了擴散阻擋特性外,還透過在銅奈米線上直接生長石墨烯或在MoS2和TaS2膜上沉積超薄銅膜,對銅/二維阻擋雜化系統的電阻率進行了嚴格檢查。透過比較有無二維介面的銅電阻率,發現當引入二維介面時,縮放銅互連器件的電阻率始終較低,這對於抑制縮放互連中銅電阻率增加的趨勢具有重要價值。

圖4. 二維場效應電晶體的接觸電阻和摻雜。

圖源: Nat Electron 4, 786–799 (2021).

非馮諾依曼架構

二維材料在如神經形態和仿生計算等後馮·諾依曼計算架構中也具有非凡的潛力。記憶體和邏輯的物理分離是馮·諾依曼計算的一個關鍵瓶頸,可以透過使用記憶交叉條結構和人工神經網路進行記憶體計算來繞過這一瓶頸。在這種情況下,利用相變、空位或離子遷移、晶粒邊界移動以及與吸附物種的偶極相互作用的二維憶阻器件的最新發現是很有前景的。此外,基於二維場效應電晶體仿生器件也得到了實驗的實現。例如,穀倉貓頭鷹的聽覺皮層可以使用分閘MoS2場效應電晶體模擬,人腦的視覺皮層可以使用共面多閘MoS2場效應電晶體模擬,蝗蟲中用於碰撞檢測的小葉巨大運動檢測器神經元的逃逸反應可以使用可程式設計MoS2場效應電晶體模擬。此外,光學活性二維材料允許實現光電突觸和智慧感測器。其他神經功能,如神經遞質釋放、短期和長期可塑性、尖峰時間依賴性可塑性、神經編碼、機率計算等,也可以使用具有高能量效率的二維人工突觸實現。

下一代感測器

二維材料憑藉其高的表面體積比,是利用表面相互作用的感測器應用的極佳候選。例如,基於MoS2的pH感測器、金屬離子汙染物感測器和葡萄糖感測器是二維化學感測器的一些典型例子,其中目標分子通常透過範德華相互作用進行物理吸附或化學吸附到缺陷位置。二維材料也可以用奈米粒子修飾,以確保更好的電化學效能、選擇性和靈敏度。生物分子,如多巴胺、抗壞血酸、尿酸、核酸(DNA和RNA)和各種抗原,也可以使用二維材料進行檢測。這種材料工作原理是目標分子和二維材料之間的電荷轉移,可以被廣泛用作氣體感測器。此外,這些二維材料還具有熱電應用的潛力。在熱電應用中,產生的廢熱可以透過二維材料轉化為電能以支援物聯網裝置。

圖5.高κ電介質在二維半導體上的整合。

圖源: Nat Electron 4, 786–799 (2021).

總結

總而言之,本文系統總結了二維材料的生長、製造和加工方面的進展,並概述了在縮放器件尺寸下二維場效應電晶體效能保證的關鍵器件引數。文章指出,接觸電阻、摻雜、高κ介電整合和器件可靠性是規模化二維場效應電晶體的主要挑戰。文章認為,在現有的矽平臺上直接生長高結晶和無缺陷的二維過渡金屬二鹵化物,以及從生長基板進行清潔和無損傷的晶圓級轉移,是進一步研究的重點領域,這將幫助二維場效應電晶體納入未來的超大規模積體電路技術。前端(FEOL)替換和/或增強需要高效能二維場效應電晶體,但後端(BEOL)整合對電晶體的要求相對寬鬆一些,但是它仍然需要二維材料的低溫生長。另一種替代方法是三維異構整合。面向未來,文章認為,二維場效應電晶體將在傳統數字、模擬和射頻電子學以及非傳統計算、感測和各種形式的易失性和非易失性儲存器中的發揮出重要的作用。

參考文獻:

Das, S., Sebastian, A., Pop, E. et al. Transistors based on two-dimensional materials for future integrated circuits. Nat Electron 4, 786–799 (2021).