記憶體是PC配件中結構最簡單的,但在BIOS中卻是最難調的,很多玩家超頻都卡在記憶體上。希望能透過對DRAM基本原理以及時序的介紹,在記憶體設定以及XMP的製作上有所幫助。

記憶體條的時序是什麼:時序及相關概念

以下把時序分為兩部分,只是為了下文介紹起來作為歸類,非官方分類方法。

第一時序:CL-tRCD-tRP-tRAS-CR,就是我們常說的5個主要時序。

第二時序:(包含所有XMP時序)

在講時序之前,我想先讓大家明白一些概念。記憶體時鐘訊號是方波,DDR記憶體在時鐘訊號上升和下降時各進行一次資料傳輸,所以會有等效兩倍傳輸率的關係。例如DDR3-1333的實際工作頻率是666.7MHz,每秒傳輸資料666.7*2=1333百萬次,即1333MT/s,也就是我們說的等效頻率1333MHz,再由每條記憶體位寬是64bit,那麼它的頻寬就是:1333MT/s*64bit/8(8bit是一位元組)=10667MB/s。所謂時序,就是記憶體的時鐘週期數值,脈衝訊號經過上升再下降,到下一次上升之前叫做一個時鐘週期,隨著記憶體頻率提升,這個週期會變短。例如CL9的意思就是CL這個操作的時間是9個時鐘週期。

另外還要搞清楚一些基本術語:

Cell:顆粒中的一個數據儲存單元叫做一個Cell,由一個電容和一個N溝道MOSFET組成。

Bank:8bit的記憶體顆粒,一個顆粒叫做一個bank,4bit的顆粒,正反兩個顆粒合起來叫做一個bank。一根記憶體是64bit,如果是單面就是8個8bit顆粒,如果是雙面,那就是16個4bit的顆粒分別在兩面,不算ECC顆粒。

Rank:記憶體PCB的一面所有顆粒叫做一個rank,目前在Unbuffered桌上型電腦記憶體上,通常一面是8個顆粒,所以單面記憶體就是1個rank,8個bank,雙面記憶體就是2個rank,8個bank。Bank與rank的定義是SPD資訊的一部分,在AIDA64中SPD一欄可以看到。

DIMM:指一條可傳輸64bit資料的記憶體PCB,也就是記憶體顆粒的載體,算上ECC晶片,一條DIMM PCB最多可以容納18個晶片。

第一時序

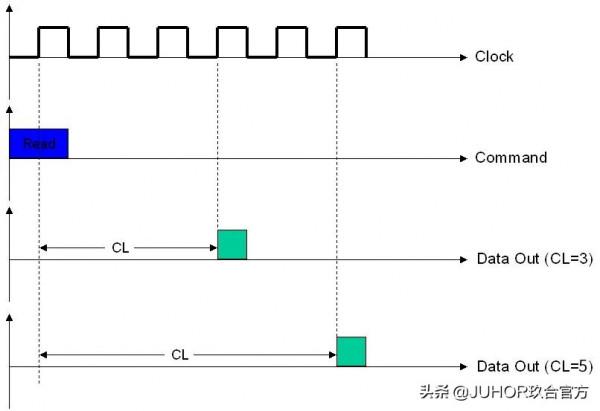

CAS Latency(CL):CAS即Column Address Strobe,列地址訊號,它定義了在讀取命令發出後到資料讀出到IO介面的間隔時間。由於CAS在幾乎所有的記憶體讀取操作中都會生效(除非是讀取到同一行地址中連續的資料,4bit顆粒直接讀取間隔3個地址,8bit顆粒直接讀取間隔7個地址,這時候CAS不生效),因此它是對記憶體讀取效能影響最強的。如下圖,藍色的Read表示讀取命令,綠色的方塊表示資料讀出IO,中間間隔的時間就是CL。

已知CL時鐘週期值CAS,我們可以使用以下公式來計算實際延遲時間tCAS:

tCAS(ns)=(CAS*2000)/記憶體等效頻率

例如,DDR3-1333 CL9記憶體實際CAS延遲時間=(9*2000)/1333=13.50 ns

或者反過來算,假如已知你的記憶體可以在7.5ns延遲下穩定工作,並且你想要DDR3-2000的頻率,那麼你可以把CL值設為8T(實際上8ns,大於7.5ns即可),如果你想要DDR3-1600的頻率,那麼你的CL值可以設到6T(實際7.5ns)。

這個公式對於所有用時鐘週期表示延遲的記憶體時序都可以用。

說到這個公式,我想順便說說大家對頻率和時序的糾結問題。首先來回顧一下DDR一代到三代的一些典型的JEDEC規範,並按照上邊那個公式算一下它的CL延遲時間:

DDR-400 3-3-3-8:(3*2000)/400=15 ns

DDR2-800 6-6-6-18:(6*2000)/800=15 ns

DDR3-1333 9-9-9-24:剛才算了是13.5 ns

再來看看每一代的超頻記憶體的最佳表現(平民級,非世界紀錄):

DDR1 Winbond BH-5 DDR-500 CL1.5:(1.5*2000)/500=6 ns

DDR2 Micron D9GMH DDR2-1400 CL4:(4*2000)/1400=5.71 ns

DDR3 PSC A3G-A DDR3-2133 CL6:(6*2000)/2133=5.63 ns

發現什麼?不管是哪一代記憶體,隨著頻率提升,CL週期也同步提升,但是最後算出來的CL延遲時間卻差不多。那麼到了DDR4,JEDEC規範頻率去到DDR4-4266,如果按照差不多的延遲,那麼按照13ns多一些來算,那麼CL值將達到28T!如果按照極限超頻延遲來算,DDR4-4266下的延遲也將達到12T。

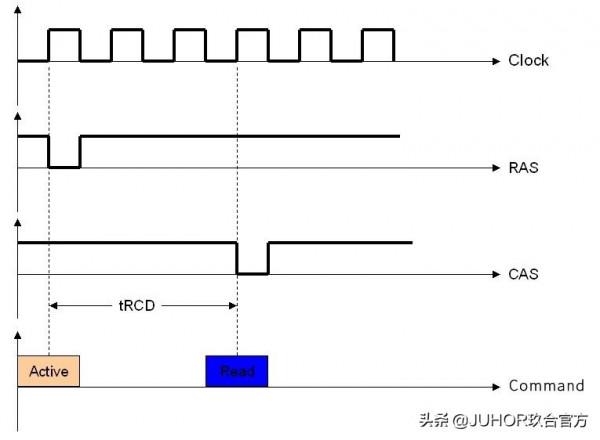

DRAM RAS to CAS Delay(tRCD):RAS的含義與CAS類似,就是行(Row)地址訊號。它定義的是在記憶體的一個rank(記憶體的一面)之中,行地址啟用(Active)命令發出之後,記憶體對行地址的操作所需要的時間。每一個記憶體cell就是一個可儲存資料的地址,每個地址都有對應的行號和列號,每一行包含1024個列地址,當某一行地址被啟用後,多個CAS請求會被髮送以進行讀寫操作。簡單的說,已知行地址位置,在這一行中找到相應的列地址,就可以完成定址,進行讀寫操作,從已知行地址到找到列地址過去的時間就是tRCD。當記憶體中某一行地址被啟用時,我們稱它為“open page”。在同一時刻,同一個rank可以開啟8個行地址(8個bank,也就是8個顆粒各一個)。下圖顯示一個行地址啟用命令發出,到尋找列地址併發出讀取指令,中間間隔的時間就是tRCD。tRCD值由於是最關鍵的定址時間,它對記憶體最大頻率影響最大,一般想要上高頻,在加電壓和放寬CL值不奏效的時候,我們都要放寬這個延遲。

DRAM RAS Precharge Time(tRP):RAS預充電時間。它定義的是前一個行地址操作完成並在行地址關閉(page close)命令發出之後,準備對同一個bank中下一個行地址進行操作,tRP就是下一個行地址啟用訊號發出前對其進行的預充電時間。由於在行地址關閉命令發出之前,一個rank中的多個行地址可能正在被讀寫,tRP對記憶體效能影響不如CL和tRCD。雖然tRP的影響會隨著多個行地址啟用與關閉訊號頻繁操作一個bank而加大,但是它的影響會被bank interleaving(bank交叉操作)和command scheduling(命令調配)所削弱。交叉讀寫會交替使用不同的bank進行讀寫,減少對一個bank的操作頻率;命令調配則是由CPU多執行緒訪問不同的記憶體地址,同樣是減少對一個bank的頻繁操作次數。例如SNB CPU的記憶體控制器可以對讀寫操作命令進行有效地重新分配,以使得行地址啟用命中率最大化(如果重複啟用一個已經處於啟用狀態的行地址,那就是RAS啟用命令未命中),所以tRP在SNB平臺對效能的影響不大,並且放寬它有可能可以幫助

第二時序——XMP

DRAM CAS Write Latency(tWCL):列地址寫入延遲,也就是DRAM的最小寫入操作時間,與CL剛好是讀寫對應關係,一般跟CL值設為同一個值就是可以穩定的。由於記憶體讀取之前必須先寫入,所以這個值可以說與CL一樣重要。但是在BIOS裡一般沒得設定,可能是與CL綁定了。

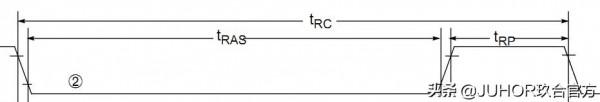

DRAM Row Cycle Time(tRC):行週期時間。定義了同一bank兩次行啟用命令所間隔的最小時間,或者說是一個bank中完成一次行操作週期(Row Cycle)的時間,即tRP+tRAS(預充電加上啟用的整個過程),tRC設得太緊可能會直接點開不了機,一般只要能進系統再多加一兩個週期都是可以穩定的。下圖顯示的就是tRC的時間。

DRAM Row Refresh Cycle Time(tRFC):行地址重新整理週期,定義了一個bank中行地址重新整理所需要的時間。重提一下重新整理的含義,由於cell中電容的電荷在MOSFET關閉之後一段時間就會失去,為了維持資料,每隔很短一段時間就需要重新充電。這裡多提一句,Intel平臺和AMD平臺對tRFC的含義不一樣,AMD平臺的tRFC是DRAM重新整理延遲時間,單位是ns,通常有90/110/160/300幾個值可以調整,也就是說它的tRFC時鐘週期會隨著頻率的提升而提升;而Intel平臺的單位則直接是時鐘週期,相反地延遲時間會隨著頻率的提升而降低。容量大的bank行地址和cell會更多,重新整理時間也更長,因此tRFC也要更高。另外,tRFC如果太快會導致資料出錯,太慢則影響效能,但可以增加穩定性。

DRAM Refresh Interval(tREFI):記憶體重新整理時間間隔,也就是記憶體的重新整理命令生效前要經過的時間。重新整理的時間間隔一般取決於記憶體顆粒的容量(density),容量越大,就越需要頻繁重新整理,tREFI值就要越低。另外tREFI的時間也會受到記憶體工作溫度與記憶體電壓(Vdimm)影響,因為溫度越高電容漏電越快。一般在AMD主機板的BIOS裡,這個值只有3.9us和7.8us可選,而在SNB平臺,則是按時鐘週期算,例如DDR3-1333下預設值為5199T,換算過來就是2000/1333x5199=7800ns,也就是7.8us。一般DRAM顆粒的spec中都是規定工作溫度大於85度時採用3.9us。

DRAM RAS to RAS Delay(tRRD):行地址間延遲,定義的是同一rank不同bank間兩個連續啟用命令的最短延遲,在DDR3時代一般最小是4T。它的作用和CR有點像,不過比CR更多的時候對效能有較大的影響,所以這個時序可儘量縮小。

DRAM Write Recovery Time(tWR):記憶體寫入恢復時間,它定義了記憶體從寫入命令發出(從開始寫入算起)到下一次預充電間隔的時間,也就是tRP的前一個操作。如果這個時間設得太短,可能會導致前一次寫入未完成就開始下一次預充電,進行定址,那麼前一次寫入的資料就會不完整,造成丟資料的情況。這個週期也是第二時序中比較長的,DDR3-2000一般需要10-14個週期,甚至更高。

DRAM Read to Precharge Time(tRTP):與tWR類似,定義了同一rank上記憶體從讀取命令發出到tRP之前的間隔時間,但是它在讀取完成並且行地址關閉之後才會生效。單顆128MB的記憶體顆粒可以在DDR3-2000下執行在4到6個時鐘週期,如果bank容量增大時,這個時序有可能要放寬。

DRAM Four Active Window(tFAW):它定義了同一rank中允許同時傳送大於四個行啟用命令的間隔時間,因此最小值應該不小於tRRD的四倍。在DDR3上,tRRD的最小值是4T,因此tFAW的最小值就是16T。這個tFAW由於是在一個rank中大於四個bank同時啟用之後才生效,因此在記憶體不是很繁忙的時候,它對效能的影響並不是很大。但是對一些頻繁讀寫記憶體的操作(例如SuperPI 32M),tFAW對效能的影響可能會加大。由於現在記憶體用滿的機率非常非常小,兩根雙面的記憶體更是有4個rank,配合上interleaving,一個rank中同時啟用大於四個bank的機率應該不大,所以通常我們把它設為tRRD的四倍應該就不會出問題。

DRAM Write to Read Delay(tWTR):記憶體寫-讀延遲,它定義的是記憶體寫入命令發出後到下一個讀取命令之間的時間間隔,最小為4T,與tRTP類似,提升記憶體的頻率或者容量提升時,這個值需要提高。

總結以上內容,我們已經對時序有了個大致的瞭解,知道一些時序設定時要注意什麼了。比如tFAW要設為tRRD的四倍,tRAS不能設太低等。記憶體是輔助CPU超頻的,時序設定只是為了放開記憶體更多的超頻空間,時序本身對效能的影響很小,並且隨著頻率的提升,或者bank數的增加,這種影響可能會進一步減小。具體不同的記憶體顆粒也會有不同的設定情況